Isi kandungan:

- Pengarang John Day day@howwhatproduce.com.

- Public 2024-01-30 11:07.

- Diubah suai terakhir 2025-01-23 15:00.

JDM adalah pengaturcara PIC yang popular kerana menggunakan port bersiri, komponen minimum dan tidak memerlukan bekalan kuasa. Tetapi ada kekeliruan di luar sana, dengan banyak variasi programmer di internet, mana yang berfungsi dengan PIC mana? Dalam "petunjuk" ini kami menguji JDM dan saya menunjukkan bagaimana mensimulasikan litar menggunakan Spice yang akan menjawab semua soalan anda!

Bekalan

LTspice yang boleh dimuat turun dari Analog Devices di sini.

Anda juga memerlukan fail litar JDM di sini.

Langkah 1: Keperluan Pelabuhan Bersiri

JDM memerlukan port bersiri yang memenuhi spesifikasi EIA232, sesuai dengan tahap Voltan + 12 / -12.

Menurut lembar data Texas Instruments Line Driver MC1488 (Rajah 3)

Impedans output = 4V / 8mA = 500 ohm.

Had arus litar pintas = 12mV, tanpa had masa - tidak ada kerosakan pada cip.

Input impedansi penerima talian = 3k hingga 7k ohm disyorkan.

Port bersiri pada PC desktop yang lebih tua menggunakan + 12v / -12V yang memenuhi syarat ini.

Port bersiri pada komputer riba yang lebih baru menggunakan voltan yang lebih rendah. JDM mungkin atau tidak berfungsi - jawapannya lebih kompleks.

Langkah 2: Keperluan Pengaturcaraan PIC

Maklumat mengenai keperluan pengaturcaraan PIC diperoleh dari Microchip. Perkara di atas adalah untuk peranti biasa.

Langkah 3: Spesifikasi JDM

Adakah laman web JDM yang asal telah hilang dalam masa yang sama? Ini membuat kita dapat meneka apa yang awalnya dimaksudkan oleh pereka untuk spesifikasi.

- Berikan VDD = 5V, dan maksimum IDD = 2mA maksimum (untuk versi "dalam soket")

- Berikan VHH = 13V, dan maksimum IHH = 0.2mA maksimum.

- MCLR Rise time tVHHR = 1uS maks.

- Versi ICSP mesti dapat menarik MCLR rendah berbanding penarikan 22k pada sasaran.

Langkah 4: Penerangan Litar

Gambar JDM1 berdasarkan litar JDM “standard” yang diambil dari laman web PICPgm. Ini adalah programmer "PIC in Socket" di mana PIC mengambil kuasa dari pin TX dan RTS. Gambar rajah asal sukar difahami jadi saya telah melukisnya semula menggunakan konvensional aliran arus dari atas ke bawah. Dan saya telah menambahkan petunjuk LED "RESET", "PROG" dan "RTS" yang diperlukan semasa pembinaan dan ujian. Semoga perkara ini tidak memberi kesan buruk kepada tingkah laku.

Konvensyen reka bentuk litar biasa adalah sama untuk semua landasan, tetapi ciri utama JDM adalah bahawa tanah port bersiri (GND) disambungkan ke VDD. Ini menimbulkan kekeliruan kerana isyarat port bersiri diukur berkenaan dengan GND, isyarat PIC berkenaan dengan landasan logik (VSS).

Apabila TX naik tinggi, Q1 berkelakuan sebagai dua diod bias ke hadapan. (Pengumpul Q1 tidak terbalik sebaliknya seperti operasi transistor biasa). Pengumpul Q1 mengenakan C2, yang dijepit pada VDD + 8V oleh Zener (D3). Pemancar Q1 memberikan 13V ke MCLR untuk Program / Mod Verifikasi.

Apabila TX menjadi rendah, kapasitor C3 dicas melalui D1 dan VSS dijepit pada VDD-5V oleh zener (D5). Juga TX dijepit pada (VSS-0.6) oleh D1. Q1 dimatikan, C1 menahan caj untuk nadi pengaturcaraan seterusnya. MCLR dijepit pada 0V oleh D2, jadi PIC kini diatur semula.

Apabila RTS tinggi, jam dihantar ke PGC. D4 pengapit PGC pada logik VDD tinggi. Apabila RTS rendah, kapasitor C3 dicas melalui D6 dan VSS dijepit pada VDD-5V oleh zener (D5). D6 mengepit PGC pada VSS atau logik 0.

Semasa pengaturcaraan, data yang dikirim pada DTR dibaca di PGD, yang dikonfigurasikan oleh PIC sebagai input. Apabila DTR tinggi, Q2 bertindak sebagai "pengikut pemancar" dan voltan PGD kira-kira (VDD-0.6) atau logik 1. Apabila DTR rendah, Q2 bertindak sebagai transistor yang buruk (pin pemancar dan pengumpul terbalik). Q2 menarik PGD rendah, yang dijepit oleh D7 pada VSS atau logik 0.

Semasa mengesahkan PIC mengkonfigurasi PGD sebagai output untuk menghantar data ke port bersiri. DTR mesti ditetapkan tinggi, dan data dibaca di CTS. Apabila output PGD tinggi, Q2 mati, CTS = DTR = + 12V. Apabila output PGD rendah, Q2 dihidupkan. Pemungut Q2 menarik arus (12V + 5V) / (1k + 1k5) = 7mA dari DTR, dan menarik CTS rendah, ke VSS.

Langkah 5: Bersedia untuk Simulasi

Muat turun rempah LT, simpan dan buka fail litar (*.asc) yang disediakan di sini. Untuk mensimulasikan litar, kita mesti memberikannya beberapa input, kemudian "jejak" outputnya. V1, V2 V3 mensimulasikan port bersiri 12V dengan impedans output R11, R12, R13.

- V1 menghasilkan 2 Denyut Program pada TX dari 0.5ms hingga 4.5ms

- V2 menghasilkan ledakan pulsa data pada DTR dari 1.5 hingga 4.5ms

- V3 menghasilkan ledakan denyutan jam pada RTS dari 0.5 hingga 3.5ms

Komponen V4, X1, R15 dan R16 semuanya merupakan bahagian simulasi.

- V4 menghasilkan 2 denyutan dari 2.5 hingga 4.5ms untuk mengesahkan data.

- Jumper X1 mensimulasikan OUTPUT pada PGD.

- R15, R16 mensimulasikan "pemuatan" PIC pada VDD dan MCLR.

Langkah 6: Pengubahsuaian untuk ICSP

Gambar JDM3 menunjukkan versi untuk pengaturcaraan "dalam litar". Pengubahsuaian dari asal adalah

- Ganti soket ZIF dengan penyambung ICSP.

- PIC kini dikuasakan oleh rangkaian bekalan ke sasaran (V5).

- Keluarkan zener 5V (D5).

- Kapasitor 100pF kecil (C4) digerakkan di sebelah PIC pada litar sasaran.

- LED mengambil kuasa dari papan litar jika boleh.

- Perintang penarik MCLR (R10) dan diod (D10) diperlukan pada litar sasaran.

- AMARAN. Papan sasaran mesti mempunyai bekalan "terapung", idealnya bateri.

- Jangan sambungkan ground target (VSS) ke ground komputer / PC dengan menghubungkan port komputer lain pada masa yang sama dengan JDM.

Setelah mensimulasikan JDM1, masalah masa pengecasan lama pada C2 menjadi jelas. Kemudian setelah membaca Fruttenboel nampaknya C2 dan Q1 ditambahkan sebagai pengubahsuaian pada yang asli. Saya tidak dapat memikirkan apa yang dimaksudkan oleh C2 dan Q1 selain daripada menimbulkan masalah. Oleh itu, untuk JDM4, kami beralih kepada reka bentuk lama pada Fruttenboel yang ringkas dan mudah difahami. D1 dan D3 / LED2 pengapit MCLR antara VSS dan VDD + 8V. Nilai R1 dikurangkan menjadi 3k3, cukup untuk menerangi LED2 pada 12V.

JDM4 juga dirancang untuk berfungsi dengan port bersiri yang lebih lemah. Apabila TX naik tinggi (+ 9V), sumber arus TX = (9-8) / (1k + 3k3) = 0.2ma, cukup untuk menarik MCLR tinggi walaupun tidak mencukupi untuk menerangi LED2. Apabila TX menjadi rendah (kira-kira -7V), sink arus TX = (9-7) / 1k = 2mA. Arus LED1 = (7-2 untuk led) / (2k7) = 1.8mA. Arus tarik MCLR = 7-5.5 / 3k3 = 0.5mA.

Litar ini juga telah diuji (simulasi JDM5) untuk melihat apa yang berlaku dengan port bersiri minimum +/- 7V, di mana voltan tidak mencukupi untuk menampung VHH = 13V. Tujuan C1 kini menjadi jelas, C1 membuat dorongan + ve pendek ke MCLR, lonjakan 33us di tepi TX yang meningkat, cukup lama untuk PIC memasuki mod pengaturcaraan, mungkin? Tetapi keluarkan pelompat X2 (matikan LED1) kerana arus tidak mencukupi untuk menarik MCLR rendah dan menerangi LED1 bersama-sama. Apabila TX menjadi rendah, sink arus TX = (7V-5.5V) / (1k + 3k3) = 0.3mA, cukup untuk menarik MCLR rendah berbanding pull-up R10.

Langkah 7: Hasil Simulasi

Untuk melihat fail grafik, lebih baik klik kanan pautan di bawah, lalu pilih "Buka pautan di Tab Baru"

Simulasi 1: jejak MCLR, VSS, dan RTS untuk JDM1 asal. Pemerhatian 1, 2 dan 3 segera kelihatan.

Simulasi 2: jejak MCLR dan VSS, dan RTS untuk JDM2 yang diubah, yang menyelesaikan masalah sebelumnya.

Simulasi 3: jejak PGD, VSS dan PGC untuk JDM2 menghantar data dalam mod program. Pemerhatian 4 pada 3.5mS.

Simulasi 4: jejak PGD, VSS dan CTS untuk JDM2 dalam mod verifikasi (pelompat X1 dimasukkan). okey

Simulasi 5: jejak MCLR, VSS, PGD dan PGC untuk JDM3. ICSP menggunakan kuasa dari litar menyelesaikan banyak masalah.

Simulasi 6: jejak MCLR, VSS, PGD dan PGC untuk JDM4 dengan port bersiri +/- 9V. MCLR segera meningkat, berfungsi sepenuhnya.

Simulasi 7: jejak MCLR, VSS, dan TX untuk JDM5 dengan port bersiri +/- 7V dan pelompat X2 dikeluarkan. C1 membuat peningkatan + ve (lonjakan) di tepi MCLR yang meningkat, cukup untuk mendorong MCLR di atas TX ke 13V.

Langkah 8: Kesimpulan

Rempah-rempah sangat baik dalam mengungkapkan "rahsia tersembunyi" operasi litar. Jelas litar JDM berfungsi dan serasi dengan banyak cip PIC, tetapi pemerhatian berikut menunjukkan kemungkinan had / keserasian masalah / kesalahan?

- Masa kenaikan MCLR yang panjang sementara C2 dikenakan ke VPP pada nadi pertama TX. Gagal spesifikasi 3.

- Port bersiri mengenakan C2 apabila TX naik tinggi dan RTS rendah. Tetapi RTS juga mempunyai tugas untuk mengecas C3. Apabila kedua-duanya berlaku pada masa yang sama ini menimbulkan lebih banyak beban pada RTS, akibatnya C3 kehilangan cas (VSS naik) pada 2ms pada simulasi. Gagal spesifikasi 1.

- C3 kehilangan cas (VSS mula naik) setelah denyutan jam berhenti pada 3.5ms.

- Apa tujuan C2, diperlukan sama sekali?

Penyelesaian

- Agaknya PICPgm menggunakan perisian "pusingan kerja". Ia mesti menggunakan nadi TX yang panjang untuk mengisi semula ke C2, kemudian hanya memasuki mod pengaturcaraan selepas nadi TX kedua? Untuk simulasi, saya mengurangkan nilai C2 menjadi 1uF untuk memberi masa kenaikan 1ms. Bukan penyelesaian yang ideal.

- Pisahkan C2 dan C3 sehingga mereka mengecas secara bebas. Satu pengubahsuaian kecil untuk JDM2, C2 dirujuk ke GND dan bukannya VSS.

- Diselesaikan oleh JDM3. ICSP jauh lebih dipercayai kerana PIC dikuasakan oleh litar sasaran.

- JDM4 menyelesaikan masalah 1. Ini adalah reka bentuk langsung yang menghilangkan C2 sama sekali.

Langkah 9: Dan Akhirnya

Buktinya puding ada pada pemakanan. JDM ini berfungsi jadi terus menggunakannya.

Dan cadangan saya adalah:

- gunakan JDM2 untuk dalam pengaturcaraan soket dan port bersiri 12V,

- gunakan JDM4 untuk programmer ICSP dan port bersiri di atas +/- 9V,

- gunakan JDM4 dengan pelompat X2 dikeluarkan untuk port bersiri di atas +/- 7V.

Rujukan:

Peranti Analog Rempah LT

picpgm

Fruttenboel

Ikuti lebih banyak projek PIC di sudut sly

Disyorkan:

Ulasan Elegoo Super Started Kit Uno R3: 4 Langkah

Ulasan Elegoo Super Started Kit Uno R3: Beberapa hari yang lalu Elegoo menghantar saya Super Starter Kit ini untuk ujian. Oleh itu, mari kita lihat apa yang ada di dalamnya. Semasa membuka kotak ringkas ini, kita dapat melihat banyak barang. Di sampul terdapat indeks dengan semua komponen. Di dalamnya kami mempunyai kad terima kasih dengan semua

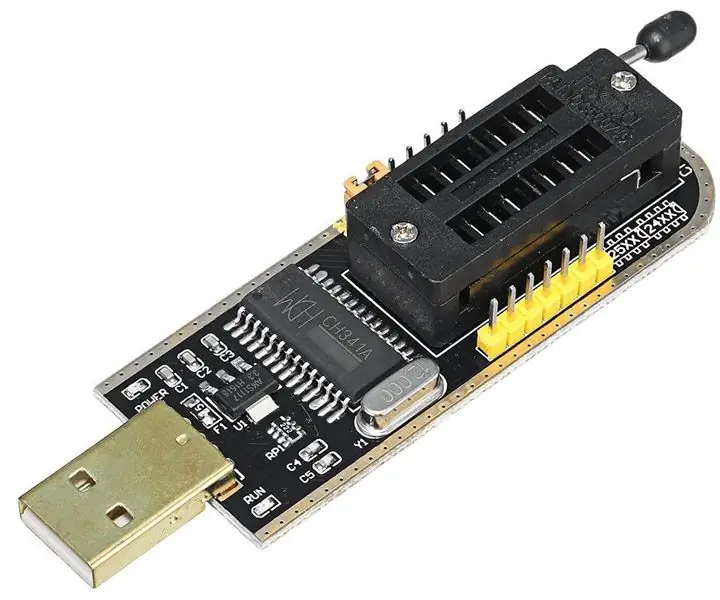

Pengaturcara CH341A: 8 Langkah

Pengaturcara CH341A: Saya baru-baru ini telah membeli pengaturcara mini CH341A. Pengaturcara mini OK dan boleh digunakan untuk memprogram cip siri 24 dan 24. Ini adalah kos yang sangat rendah tetapi cukup berguna kerana saya dapat menggunakannya untuk mem-flash BIOS komputer saya dan firmware penghala. WCH mempunyai siaran

Arduino Sebagai ISP -- Bakar Fail Hex dalam AVR -- Fius dalam AVR -- Arduino Sebagai Pengaturcara: 10 Langkah

Arduino Sebagai ISP || Bakar Fail Hex dalam AVR || Fius dalam AVR || Arduino Sebagai Pengaturcara: ……………………… Sila Langgani saluran YouTube saya untuk lebih banyak video …….. Artikel ini adalah mengenai arduino sebagai isp. Sekiranya anda ingin memuat naik fail hex atau jika anda ingin menetapkan fius anda di AVR maka anda tidak perlu membeli programmer, anda boleh melakukan

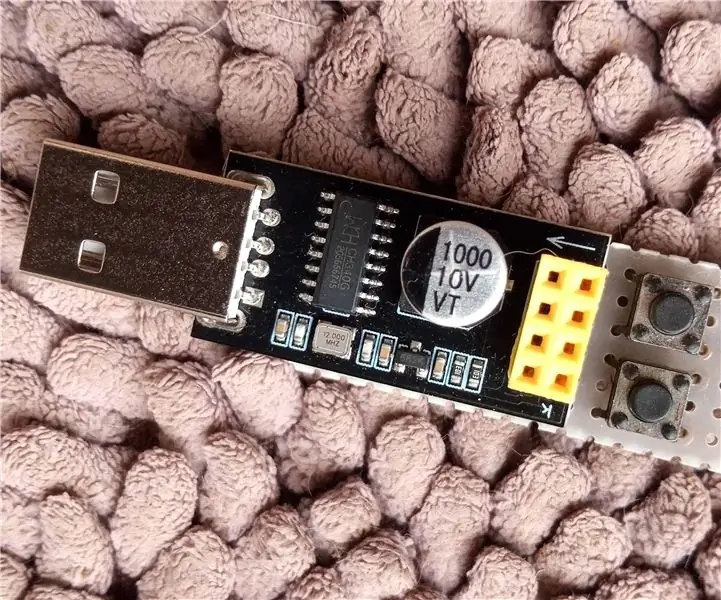

Hack Pengaturcara ESP-01 - Yang Mudah :): 6 Langkah

Hack Pengaturcara ESP-01 - Yang Mudah :): Hai ESPers, Dalam arahan ini saya akan menunjukkan peretasan mudah untuk membuat programmer untuk modul ESP-01 / ESP8266-01 / ES-01. Sebilangan besar daripada kita telah menggunakan papan Arduino atau peranti FTDI USB-TTL sebagai pengaturcara untuk modul ini. Kedua-dua kaedah ini berfungsi dengan baik. Tetapi

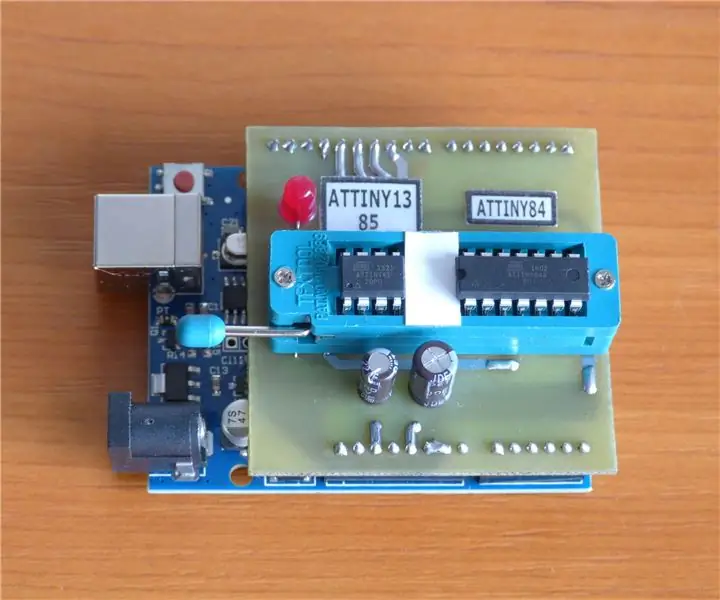

Pengaturcara Kecil untuk Pengawal Mikro ATTINY Dengan Arduino UNO: 7 Langkah

Pengaturcara Kecil untuk Pengawal Mikro ATTINY Dengan Arduino UNO: Pada masa ini menarik untuk menggunakan mikrokontroler siri ATTINY kerana fleksibiliti, harga rendah tetapi juga fakta bahawa mereka dapat diprogram dengan mudah di persekitaran seperti Arduino IDE. Program yang dirancang untuk modul Arduino dapat dengan mudah memindahkan