Isi kandungan:

- Langkah 1: Gambarajah Blok

- Langkah 2: Prinsip Operasi

- Langkah 3: Pelaksanaan Logik

- Langkah 4: Menyelesaikan Kebuntuan

- Langkah 5: Konfigurasi Peranti - Litar Matrix0

- Langkah 6: Konfigurasi Peranti - Logik Jam SPI

- Langkah 7: Konfigurasi Peranti - Sifat Komponen Matrix0

- Langkah 8: Konfigurasi Peranti - Litar Matrix1

- Langkah 9: Konfigurasi Peranti - Kaunter Binari 3-bit

- Langkah 10: Konfigurasi Peranti - Logik Bandingkan 3-bit

- Langkah 11: Konfigurasi Peranti - Logik Perbandingan Digital dan Daftar Sementara

- Langkah 12: Konfigurasi Peranti - Sifat Komponen Matrix1

- Langkah 13: Hasil

- Pengarang John Day day@howwhatproduce.com.

- Public 2024-01-30 11:08.

- Diubah suai terakhir 2025-01-23 15:00.

Sistem kawalan dan peranti yang berkaitan berurusan dengan pelbagai sumber kuasa, seperti garis bias atau bateri, dan mesti mengesan garis tertinggi (atau terendah) di antara satu set tertentu.

Sebagai contoh, peralihan beban dalam sistem bertenaga "multi bateri" memerlukan sistem memantau voltan minimum atau maksimum di antara array bateri (maks atau min sebagai fungsi dari algoritma pensuisan tertentu) dan secara dinamis mengarahkan beban ke sumber yang paling sesuai dalam masa nyata. Sebagai alternatif, sistem mungkin perlu melepaskan sementara dari bateri voltan terendah untuk pengisian yang betul.

Contoh lain adalah sistem tenaga suria moden, di mana setiap panel suria dilengkapi dengan mekanisme tiltrotate dan dengan rangkaian pengesanan suria (yang terakhir memberikan maklumat kedudukan Matahari untuk mengarahkan panel). Dengan maklumat voltan maksimum, setiap kedudukan panel suria dapat diperbaiki berdasarkan panel tali yang sebenarnya memberikan voltan keluaran tertinggi, sehingga mencapai tahap pengoptimuman daya yang lebih tinggi.

Terdapat beberapa jenama IC komersial yang berbeza (terutamanya mikrokontroler) yang pada prinsipnya dapat menerapkan pengikut voltan maksimum. Walau bagaimanapun, mereka memerlukan pengaturcaraan dan lebih murah daripada penyelesaian isyarat campuran. Melengkapkan reka bentuk Dialog GreenPAKTM secara positif dapat mempengaruhi kemampuan, ukuran, dan modulariti reka bentuk. Reka bentuk ini memanfaatkan faedah mengintegrasikan litar analog dan digital ke dalam satu cip tunggal.

Dalam Instructable ini, front-analog analog dan logik digital yang diperlukan untuk melaksanakan pencari voltan maksimum (atau akhirnya min) di antara lapan sumber berbeza dilaksanakan.

Untuk melaksanakan monitor voltan maksimum / min analog 8-saluran digunakan SLG46620G.

Di bawah ini kami menerangkan langkah-langkah yang diperlukan untuk memahami bagaimana penyelesaian telah diprogramkan untuk membuat monitor voltan maksimum / min analog 8-saluran. Namun, jika anda hanya ingin mendapatkan hasil pengaturcaraan, muat turun perisian GreenPAK untuk melihat Fail Reka Bentuk GreenPAK yang sudah siap. Pasang Kit Pembangunan GreenPAK ke komputer anda dan tekan program untuk membuat monitor voltan maksimum / min analog 8-saluran.

Langkah 1: Gambarajah Blok

Rajah 1 menunjukkan gambarajah global sistem yang dilaksanakan.

Rentetan hingga 8 sumber voltan berubah-ubah dilipatgandakan dan dihubungkan ke modul ADC GreenPAK yang disambungkan ke reka bentuk dalaman disesuaikan yang mampu memilih sumber dengan voltan tertinggi berkenaan dengan yang lain. Logik dalaman mengeluarkan maklumat ini untuk paparan atau pemprosesan selanjutnya.

Reka bentuknya didasarkan pada produk GreenPAK SLG46620G, kerana merangkumi semua blok bangunan analog dan digital yang diperlukan untuk aplikasi. Dalam pelaksanaan ini, array diimbas menggunakan multiplexer analog ADG508 yang digerakkan secara langsung oleh IC GreenPAK.

Maklumat output adalah nombor digital 3-bit yang sesuai dengan nombor sumber voltan pada voltan maksimum. Cara langsung untuk mendapatkan maklumat ini adalah dengan menunjukkan nombor melalui paparan 7 segmen. Ia dapat dicapai dengan mudah dengan menghubungkan output digital SLG46620G ke pemacu paparan 7 segmen, seperti penyelesaian GreenPAK yang dijelaskan dalam Rujukan atau ke IC 74LS47 biasa.

Litar yang ditunjukkan mencari voltan maksimum. Untuk menukar reka bentuk menjadi pencari voltan minimum, litar pra-penyaman sederhana mesti ditambah antara input analog dan input analog GreenPAK, mengurangkan output multiplexer dari voltan rujukan 1 V.

Langkah 2: Prinsip Operasi

Reka bentuk bertujuan untuk memilih sumber dengan voltan maksimum, oleh itu imbasan dilakukan pada keseluruhan array sambil menyimpan nilai terakhir-maksimum dan membandingkannya dengan nilai input seterusnya (yang termasuk sumber voltan seterusnya dalam imbasan).

Berikut ini kita akan merujuk kepada urutan multiplexing lengkap sepanjang semua input sebagai "scan" atau "loop".

Perbandingan antara dua nilai tidak dicapai dengan menggunakan komponen ACMP (namun tersedia dalam SLG46620G), melainkan dengan modul DCMP, setelah nilai masing-masing didigitalkan. Ini adalah teknik canggih dan halus yang pertama kali dibahas dalam Referensi.

Rajah 2 menunjukkan bagaimana SLG46620G disusun untuk reka bentuk ini.

Isyarat input analog menuju input ADC melalui komponen PGA dengan set Gain of 1. Pelbagai tetapan Gain juga mungkin untuk mencari padanan terbaik dengan elektronik penyaman depan yang dikhaskan untuk memetakan voltan input ke 0-1 V rangkaian modul GreenPAK ADC.

ADC beroperasi dalam mod satu hujung dan menukar isyarat analog ke kod digital 8-bit, yang kemudian dipindahkan ke modul DCMP. Kod digital juga dimasukkan ke dalam blok SPI, dikonfigurasi sebagai ADC / FSM Buffer, di mana kod digital dapat disimpan dan tidak akan berubah sehingga nadi seterusnya datang ke input SPI CLK. Perhatikan bahawa blok logik khusus memacu input SPI CLK. Kami akan menyiasat bahagian ini kemudian, kerana ini adalah "inti" logik yang bertanggungjawab untuk operasi yang betul. Kod digital baru disimpan ke dalam modul SPI hanya jika ia termasuk voltan input maksimum yang sebenarnya.

Komponen DCMP digunakan untuk membandingkan data ADC semasa dengan pemenang terakhir (iaitu max terakhir yang dijumpai) yang disimpan di blok SPI. Ia akan menghasilkan nadi pada output OUT + apabila data ADC baru lebih besar daripada yang sebelumnya. Kami menggunakan isyarat OUT + untuk mengemas kini blok SPI dengan pemenang baru.

Isyarat jam global mendorong penukaran ADC dan masa umum. Setelah penukaran dilakukan, denyut isyarat output INC ADC, diselaraskan dalam masa dengan output data selari ADC. Kami menggunakan output INT juga untuk meningkatkan pembilang binari 3-bit, yang dilaksanakan oleh DFF di Matrix1, yang berguna untuk tiga sebab:

1. Garis output kaunter mengatasi multiplexer analog luaran, dengan itu memberikan voltan input seterusnya ke ADC;

2. Kiraan dibekukan ke dalam daftar 3-bit (dilaksanakan dalam Matrix1) untuk menyimpan pemenang sementara semasa imbasan;

3. Kiraannya disahkod untuk mengemas kini daftar 3-bit kedua (dilaksanakan dalam Matrix0) setelah imbasan selesai.

Langkah 3: Pelaksanaan Logik

Modul ADC secara berurutan menyediakan data yang ditukar dari semua voltan input, satu demi satu, selama-lamanya. Setelah Multiplexer dialamatkan 0b111 (perpuluhan 7), pembilang akan berubah menjadi 0b000 (perpuluhan 0) sehingga memulakan imbasan voltan input baru.

Semasa imbasan, isyarat output ADC INT dihasilkan apabila output data selari berlaku. Apabila isyarat ini berdenyut, multiplexer analog mesti beralih ke input seterusnya, memberikan voltan yang sesuai kepada PGA. Oleh itu, output ADC INT adalah isyarat jam langsung dari Kaunter Binari 3-bit Rajah 2, yang mana perkataan output selari 3-bit secara langsung menangani multiplexer analog luaran ("pilih V" dalam Rajah 1).

Mari kita merujuk kepada contoh di mana voltan input seharusnya mempunyai hubungan berikut:

a) V0 <V1 <V2

b) V2> V3, V4

c) V5> V2

Gambar 3 menunjukkan isyarat utama yang terlibat dalam mekanisme keputusan maksimum.

Oleh kerana data akhirnya direkodkan ke daftar penyangga SPI secara serentak dengan denyut INT, tetingkap perbandingan wujud di mana kandungan penyangga SPI dibandingkan dengan hasil penukaran ADC berikutnya. Pemasaan tertentu ini menghasilkan penghasilan denyut OUT + pada output DCMP. Kami dapat memanfaatkan pulsa ini untuk memuat nilai baru ke dalam daftar penyangga SPI.

Seperti yang jelas dari garis data penyangga SPI pada Gambar sebelumnya, daftar SPI selalu berisi, dari semasa ke semasa, nilai terbesar di antara 8 input dan ia dikemas kini hanya apabila nilai yang lebih besar dikesan oleh modul DCMP (merujuk pada DCMP Garis keluaran OUT + plot, denyutan yang hilang menyebabkan V2 tetap terkunci dalam daftar sehingga dibandingkan dengan V5).

Langkah 4: Menyelesaikan Kebuntuan

Sekiranya logik yang dilaksanakan sama seperti yang dijelaskan di atas, jelas bahawa kita akan menghadapi situasi kebuntuan: sistem hanya mampu mengesan voltan yang lebih tinggi daripada yang sesuai dengan apa yang disimpan ke dalam daftar penyangga SPI.

Ini juga berlaku sekiranya voltan ini berkurang dan input lain, sehingga sekarang lebih rendah daripada itu, menjadi yang tertinggi: tidak akan dapat dikesan. Keadaan ini dijelaskan dengan lebih baik dalam Rajah 4 di mana hanya 3 voltan input yang hadir untuk kejelasan.

Pada masa lelaran 2, penurunan V3 dan V1 adalah voltan maksimum sebenar. Tetapi modul DCMP tidak memberikan nadi kerana data yang disimpan ke dalam daftar penyangga SPI (sepadan dengan 0,6 V) lebih besar daripada yang sepadan dengan V1 (0,4 V).

Sistem ini kemudian bertindak sebagai pencari maksimum "mutlak" dan tidak mengemas kini output dengan betul.

Cara yang baik untuk mengatasi masalah ini adalah dengan memaksa memuat semula data ke SPI Buffer Register apabila sistem menyelesaikan kitaran pengundian penuh semua saluran.

Sebenarnya, jika voltan pada input tersebut masih tinggi, tidak ada yang berubah dan kawalannya selamat (merujuk pada Rajah 4 di atas, ini adalah kes Loop Iterations 0 dan 1). Sebaliknya, jika voltan pada input itu secara kebetulan turun ke nilai yang lebih rendah daripada input lain, maka tambah nilai memberi kemungkinan kepada modul DCMP untuk menghasilkan denyut OUT + ketika membandingkannya dengan nilai maksimum baru (ini adalah kes Iterasi Gelung 2 dan 3).

Sepotong litar logik diperlukan untuk mengatasi masalah tersebut. Ia mesti menghasilkan isyarat jam ke komponen SPI ketika gelung mencapai input maksimum yang sebenarnya, sehingga memaksa memuat semula kata datanya yang dikemas kini ke dalam SPI Buffer Register. Perkara ini akan dibincangkan di Bahagian 7.2 dan 7.6 di bawah.

Langkah 5: Konfigurasi Peranti - Litar Matrix0

SLG46620G mempunyai dua blok Matriks, seperti yang digambarkan dalam Gambar 2. Gambar berikut menunjukkan konfigurasi peranti masing-masing.

Bahagian atas litar adalah "Loop Register" yang direalisasikan dengan 3 DFF (DFF0, DFF1, dan DFF2). Ia disegarkan selepas setiap gelung multiplexer input untuk menghantar kepada pemacu paparan 7 segmen nombor perduaan "pemenang", iaitu input dengan voltan tertinggi dalam imbasan terakhir. Jam ke DFF dan data berasal dari logik yang dilaksanakan di Matrix1 melalui, masing-masing, port P12, P13, P14, dan P15.

Bahagian bawah adalah hujung depan analog dengan input pada Pin 8 dan PGA dengan keuntungan x1. Output ADC INT masuk ke logik pemasaan SPI dan ke Matrix1 melalui port P0, di mana ia akan berfungsi sebagai isyarat jam untuk kaunter yang dilaksanakan.

Keluaran data selari ADC dan SPI masing-masing dilabel NET11 dan NET15 untuk disambungkan ke komponen DCMP di Matrix1.

Langkah 6: Konfigurasi Peranti - Logik Jam SPI

Seperti yang ditunjukkan sebelumnya di bagian "Implementasi Logik", SPI Buffer Register diperbaharui setiap kali bahawa perbandingan antara nilai tersimpan yang sebenarnya dan data penukaran ADC yang baru menghasilkan denyutan pada output DCMP OUT +.

Integriti isyarat terjamin sekiranya isyarat ini DIBUAT dengan keluaran ADC INT. Ini mengelakkan lonjakan dan pencetus palsu.

Kami juga telah menggarisbawahi bahawa untuk melangkau situasi kebuntuan, SPI Buffer mesti dikemas kini apabila gelung mencapai data pemenang sebenar.

Tiga isyarat kemudian berada dalam permainan untuk pemasaan SPI yang betul:

1. Keluaran ADC INT (LUT0-IN1)

2. DCMP OUT + output (LUT0-IN0 melalui port P10)

3. Kira sama dengan isyarat Latch (LUT0-IN2 melalui port P11)

Dua yang pertama adalah AND-ed dan kedua OR-ed dengan yang terakhir di LUT0, yang pelaksanaannya dikonfigurasi seperti pada Gambar 6.

Langkah 7: Konfigurasi Peranti - Sifat Komponen Matrix0

Gambar 7-10 menunjukkan baki tetingkap harta milik Matrix0.

Langkah 8: Konfigurasi Peranti - Litar Matrix1

Langkah 9: Konfigurasi Peranti - Kaunter Binari 3-bit

Bahagian atas litar mengandungi elemen logik, terutamanya pembilang binari 3-bit yang dicatat oleh output ADC INT, seperti yang telah dibincangkan. Pembilang ini dilaksanakan dengan skema yang agak "standard" seperti yang ditunjukkan pada Gambar 12.

Kaunter ini direalisasikan dalam reka bentuk kami dengan menggunakan Flip-Flops DFF9, DFF10, DFF11 dan INV1, LUT4, LUT8. Output DFF9 adalah LSB sementara DFF11 adalah MSB seperti yang ditunjukkan dalam Rajah 13.

LUT4 dikonfigurasikan sebagai XOR sementara LUT8 melakukan logik AND-XOR pada Rajah 12.

Keluaran penghitung pergi ke tiga pin output digital untuk mengatasi Analog Multiplexer luaran.

LUT10 menyahkod kod kaunter apabila imbasan selesai dan memberi nadi kepada Matrix0 melalui DLY8 dan port P12. Ini hanya dapat dicapai dengan AND keluarkan penghitung, sehingga penyahkodan nombor 7 dec (binari 0b111, hujung gelung).

Langkah 10: Konfigurasi Peranti - Logik Bandingkan 3-bit

Gambar 15 menunjukkan litar yang digunakan untuk mengesan ketika gelung berulang pada alamat "pemenang" semasa. Dalam kes ini, seperti yang telah dibincangkan, denyut digital harus memaksa beban semula hasil ADC semasa untuk menyelesaikan kemungkinan situasi kebuntuan.

Alamat "pemenang" disimpan di daftar sementara Matrix1 (lihat di bawah), sementara alamat semasa dikeluarkan oleh kaunter binari.

Gerbang XNOR memberikan output benar (logik 1 atau 'tinggi') apabila kedua-dua input sama. DAN menggunakan isyarat ini untuk semua bit (LUT9) memberi kita nadi apabila kedua-dua kod binari sama. Perincian mengenai gerbang XOR sebagai pemeriksa pariti boleh didapati di Rujukan.

Isyarat ‘Counter-equals-Latch’ diteruskan ke Matrix0 melalui port P11.

Langkah 11: Konfigurasi Peranti - Logik Perbandingan Digital dan Daftar Sementara

Bahagian bawah Rajah 11 (disorot dalam Gambar 16) menunjukkan blok DCMP, bahagian membuat keputusan dalam reka bentuk ini.

DFF6, 7, dan 8 membentuk register 3-bit untuk menyimpan nombor input sementara "pemenang" semasa gelung sedang berjalan. Input ke Flip-Flops adalah output pembilang binari 3-bit, seperti yang dapat dilihat dalam litar Matrix1 global Rajah 11, di sini dilangkau demi kejelasan.

Keluaran dari daftar ini tidak dapat mendorong langsung paparan 7 segmen kerana nilai yang disimpan di sini berubah semasa imbasan dan harus dianggap 'sah' hanya pada akhir imbasan itu sendiri.

Atas sebab ini, output daftar sementara menyambung ke Daftar Gelung Matrix0 melalui port antara matriks P13, P14, dan P15.

Penting untuk diperhatikan dalam Rajah 16 bahawa daftar sementara dicatat oleh output DCMP OUT + apabila ADC-SPI mendaftarkan hasil perbandingan dalam max baru yang dijumpai.

Isyarat OUT + yang sama diteruskan ke Matrix0, SPI CLK Logic, melalui port P10.

Langkah 12: Konfigurasi Peranti - Sifat Komponen Matrix1

Gambar 17-19 menunjukkan tetingkap harta komponen milik Matrix1.

Langkah 13: Hasil

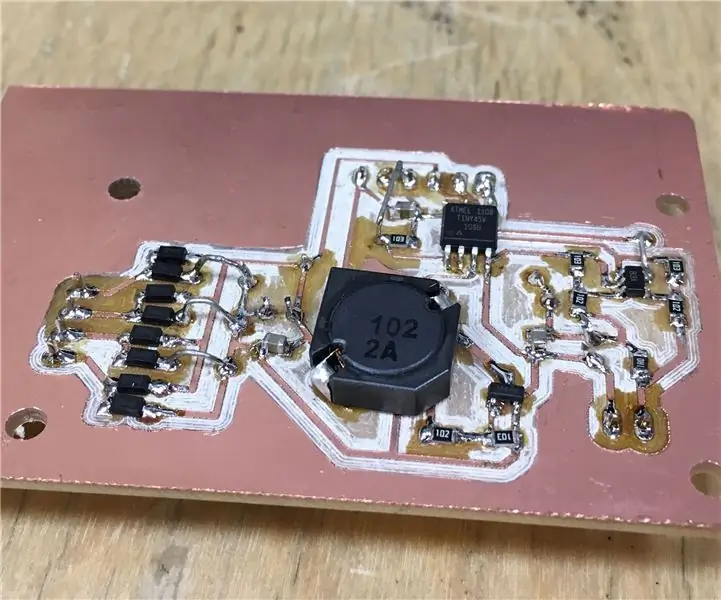

Untuk menguji pelaksanaannya, prototaip papan penilaian telah dibangun, di mana 8 voltan input analog diperoleh oleh rangkaian pembahagi perintang dengan TrimPots (seperti yang ditunjukkan pada Gambar 20).

Multiplexer yang digunakan adalah ADG508, bahagian yang boleh beroperasi dengan bekalan tunggal (12 V).

Pemacu paparan 7 segmen adalah 74LS47. Ia menyahkod kata input selari dan secara langsung mendorong paparan segmen 7-anod biasa.

Papan penilaian mempunyai penyambung sudut kanan 2x10 untuk disambungkan terus ke GreenPAK Advanced Development Platform pada penyambung pengembangannya seperti yang ditunjukkan pada Gambar 21.

Hubungan dengan Platform Pembangunan Lanjutan GreenPAK menjadikan pengukuran isyarat sangat mudah untuk diperiksa. Sebagai contoh, Rajah 22 menunjukkan satu set isyarat (masing-masing CLOCK, ADC INT output, dan DCMP OUT + output) seperti yang ditangkap oleh HP 54620A Logic Analyzer. Bentuk gelombang dipicu oleh kelebihan isyarat OUT + yang meningkat (pada ruang lingkup berlabel sebagai 'A> B'), oleh itu ini adalah tangkapan bentuk gelombang apabila Voltan maksimum baru dikesan di antara input analog. Sebenarnya, ia diperoleh dengan memutar salah satu TrimPots dari Lembaga Penilaian untuk meningkatkan voltan sepadan yang ditunjukkan dalam Rajah 22.

Rajah 23 menunjukkan skema Lembaga Penilaian.

Kesimpulannya

Dalam Instructable ini, kami menerapkan pencari voltan maksimum (atau min) lapan saluran untuk digunakan sebagai penambahan umum untuk sistem kawalan berbilang saluran. Pendekatan yang dikemukakan memanfaatkan ciri-ciri canggih dari komponen GreenPAK dan menunjukkan bagaimana mungkin untuk menyatu dalam satu fungsi analog dan digital satu cip. Beberapa IC komersial boleh diganti dengan Dialog GreenPAK sehingga ukuran dan kos aplikasi dapat dikurangkan.

Disyorkan:

Monitor Voltan untuk Bateri Voltan Tinggi: 3 Langkah (dengan Gambar)

Monitor voltan untuk bateri voltan tinggi: Dalam panduan ini saya akan menerangkan kepada anda bagaimana saya membina monitor voltan bateri saya untuk papan panjang elektrik saya. Pasang sesuka anda dan sambungkan hanya dua wayar ke bateri anda (Gnd dan Vcc). Panduan ini menganggap bahawa voltan bateri anda melebihi 30 volt, dengan

Tracker Power Point Maksimum untuk Turbin Angin Kecil: 8 Langkah

Penjejak Power Point Maksimum untuk Turbin Angin Kecil: Terdapat banyak turbin angin DIY di internet tetapi sangat sedikit yang menjelaskan dengan jelas hasil yang mereka peroleh dari segi kuasa atau tenaga. Juga sering terdapat kekeliruan antara daya, ketegangan dan arus. Banyak masa, orang mengatakan: " Saya mengukur

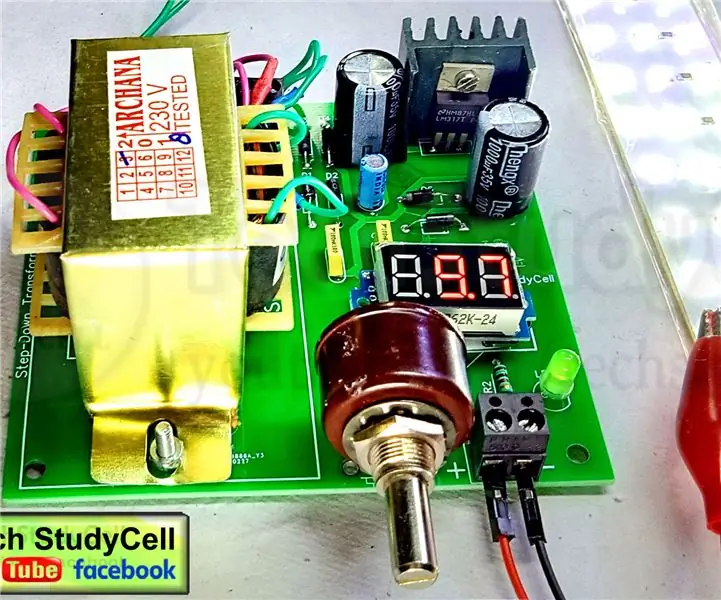

Bekalan Kuasa Voltan DC Boleh Laras Menggunakan Pengatur Voltan LM317: 10 Langkah

Bekalan Kuasa Voltan DC Boleh Laras Menggunakan Pengatur Voltan LM317: Dalam projek ini, saya telah merancang bekalan kuasa voltan mudah laras DC menggunakan IC LM317 dengan gambarajah litar bekalan kuasa LM317. Oleh kerana litar ini mempunyai penerus jambatan terbina dalam sehingga kita dapat menghubungkan bekalan AC 220V / 110V secara langsung pada input

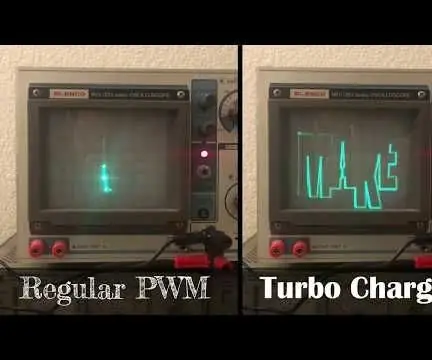

Voltan Analog Super Cepat Dari Arduino: 10 Langkah (dengan Gambar)

Voltan Analog Super Cepat Dari Arduino: Instructable ini menunjukkan cara menghasilkan perubahan voltan analog super cepat dari Arduino dan pasangan perintang dan kapasitor sederhana. Salah satu aplikasi yang berguna ini adalah menghasilkan grafik pada osiloskop. Terdapat beberapa projek lain yang

Pemindahan Bateri, Kitar Semula hingga Maksimum: 5 Langkah

Pemindahan Bateri, Kitar Semula ke Maksimum: Semasa membersihkan kedai kerja saya, saya menjumpai beberapa Bateri DeWALT yang benar-benar mati. Mereka tidak akan mengambil caj, dan memukulnya dengan voltan tinggi tidak berfungsi eter. Oleh kerana kebanyakan alat saya DeWALT mempunyai bateri tambahan sangat membantu