Isi kandungan:

- Pengarang John Day [email protected].

- Public 2024-01-30 11:09.

- Diubah suai terakhir 2025-01-23 15:01.

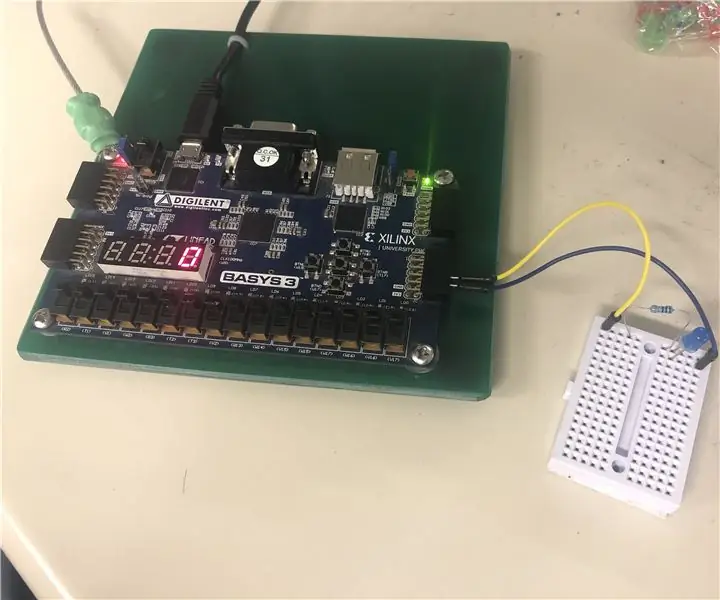

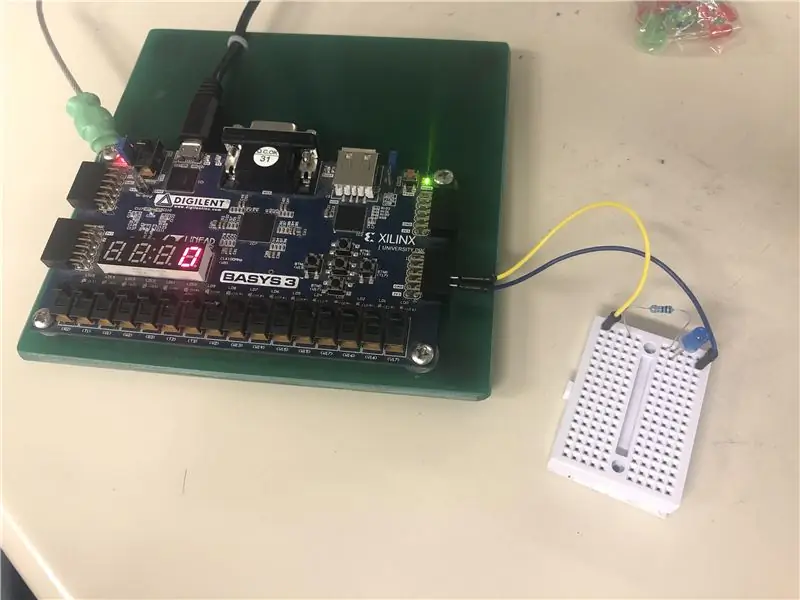

Dalam panduan ini kita akan membina dan mengawal sistem peredupan LED luaran. Dengan butang yang tersedia, pengguna dapat meredupkan mentol LED ke kecerahan yang diinginkan. Sistem ini menggunakan papan Basys 3, dan disambungkan ke papan roti yang mengandungi perintang dan mentol LED. Menekan butang "atas" yang ditentukan akan meningkatkan kecerahan, dan menekan butang "bawah" akan menurunkan kecerahan hingga sifar. Ini bukan sahaja menghalang pengguna daripada dibutakan oleh mentol terang seperti cahaya matahari tetapi juga menjimatkan tenaga!

Langkah 1: Buat Pembilang Input

Untuk langkah ini kita membuat komponen yang menentukan tahap kecerahan (melalui jam) dengan menggunakan dua suis: satu untuk meningkat dan satu untuk menurun. Dengan menggunakan VHDL, kami menghasilkan kaunter melalui penggunaan flip-flop D. Menekan butang "atas" mendorong keadaan seterusnya ke keadaan sekarang, keluar ke paparan tujuh segmen dan mentol LED.

entiti updown_counter adalah

Pelabuhan (present_state: out STD_LOGIC_VECTOR (3 downto 0); sebelumnya_state: di STD_LOGIC_VECTOR (3 downto 0); next_state: in STD_LOGIC_VECTOR (3 downto 0); clk: in STD_LOGIC; down_enable: in STD_LOGIC; up_enog: in_enog; akhir updown_counter; arsitektur Behavioral of updown_counter is start flop: process (next_state, clk, up_enable, down_enable, sebelumnya_state) bermula jika (meningkat_kebaikan (clk)) maka jika (up_enable = '1' dan tidak (next_state = "0000")) maka present_state <= negeri_ seterusnya; elsif (down_enable = '1' and not (sebelumnya_state = "1111")) kemudian present_state <= sebelumnya_state; tamat sekiranya; tamat sekiranya; proses akhir gagal; Tingkah laku akhir;

Kami juga memerlukan jam untuk setiap input dimasukkan (ketika naik), jadi kami juga membuat pembahagi jam yang menentukan seberapa cepat butang dapat ditekan di antara setiap tingkat kecerahan. Pembahagi jam ini membolehkan kita memaparkan tahap yang betul pada paparan tujuh segmen dan menghasilkan tahap intensiti yang tepat untuk setiap tahap.

entiti counter_clkDiv adalah

Port (clk: dalam std_logic; sclk: out std_logic); tamat kaunter_clkDiv; seni bina my_clk_div of counter_clkDiv adalah max_count malar: integer: = (10000000); isyarat tmp_clk: std_logic: = '0'; mulakan my_div: proses (clk, tmp_clk) pemboleh ubah div_cnt: integer: = 0; mulakan jika (meningkat_kebaikan (clk)) maka jika (div_cnt> = MAX_COUNT) maka tmp_clk <= bukan tmp_clk; div_cnt: = 0; lain div_cnt: = div_cnt + 1; tamat sekiranya; tamat sekiranya; sclk <= tmp_clk; proses akhir my_div; tamatkan my_clk_div;

Langkah 2: Buat Pembahagi Jam LED

Untuk langkah ini, kami membuat pembahagi jam untuk mentol LED untuk menentukan 16 tahap intensiti yang berbeza. Dengan 0 hingga 15 menampilkan kecerahan maksimum, pembahagi jam menambah setiap butang tekan dengan apa yang kita tetapkan menjadi tahap kecerahan. Setiap peningkatan tahap bermaksud peningkatan jam untuk lampu LED. Mengingat bahawa kecerahan tidak meningkat secara linier, kami menggerakkan jam ke tahap tertinggi yang dapat dicapai dan menurunkan jam kami dengan sewajarnya.

Catatan: kami menggunakan LED biru. Menggunakan warna yang berbeza (seperti merah) memerlukan jam yang sedikit berbeza sama sekali; tetapan kecerahan sederhana untuk biru sudah boleh menjadi kecerahan maksimum untuk warna merah. Ini berlaku kerana panjang gelombang cahaya yang berbeza akan memerlukan jumlah tenaga yang berbeza, dengan warna yang lebih sejuk seperti ungu dan biru memerlukan lebih banyak tenaga, sementara warna yang lebih panas seperti merah dan oren memerlukan lebih sedikit tenaga.

entiti led_clkDiv adalah Port (present_state: in STD_LOGIC_VECTOR (3 downto 0); clk: in STD_LOGIC; led_clk: out STD_LOGIC); tamat led_clkDiv; seni bina Tingkah laku led_clkDiv adalah isyarat tmp_clk: std_logic: = '0'; pemboleh ubah dikongsi max_count: integer; begin count_stuff: process (present_state) begin case present_state adalah ketika "0000" => max_count: = 0; apabila "0001" => max_count: = 2; apabila "0010" => max_count: = 4; apabila "0011" => max_count: = 6; apabila "0100" => max_count: = 8; apabila "0101" => max_count: = 10; apabila "0110" => max_count: = 12; apabila "0111" => max_count: = 14; apabila "1000" => max_count: = 16; apabila "1001" => max_count: = 25; apabila "1010" => max_count: = 50; apabila "1011" => max_count: = 100; apabila "1100" => jumlah maksimum: = 150; apabila "1101" => jumlah maksimum: = 200; apabila "1110" => jumlah maksimum: = 250; apabila "1111" => jumlah maksimum: = 300; kes akhir; proses akhir hitungan_bahan; my_div: proses (clk, tmp_clk, present_state) pemboleh ubah div_cnt: integer: = 0; mulakan jika (meningkat_kebaikan (clk)) maka jika (div_cnt> = max_count) maka tmp_clk <= bukan tmp_clk; div_cnt: = 0; lain div_cnt: = div_cnt + 1; tamat sekiranya; tamat sekiranya; led_clk <= tmp_clk; proses akhir my_div; Tingkah laku akhir;

Langkah 3: Membuat Pengawal LED

Sekarang kita berjaya sejauh ini, tiba masanya untuk menggabungkan semua komponen yang telah kita buat sejauh ini ke dalam fail Pengawal LED.

Ringkasnya, komponen yang digunakan adalah seperti berikut:

- Pembilang input (updown_counter)

- Pembahagi jam (counter_clkDiv)

- Pembahagi jam LED (led_clkDiv)

- Pemacu paparan tujuh segmen (sseg_dec) (fail terlampir)

Pemacu paparan tujuh segmen sebenarnya tidak pernah dibincangkan sebelum ini kerana kami sebenarnya meminjam fail VHDL dari Dr. Bryan Mealy kerana kodnya yang panjang dan rumit. Yang pada dasarnya adalah mendorong input butang kami ke paparan tujuh segmen di papan Basys 3 sehingga kita tahu tahap kecerahan.

Melangkah ke hadapan, Pengawal LED menggunakan flip flop untuk meningkatkan atau mengurangkan kiraan yang mengawal paparan tujuh segmen dan tahap kecerahan mentol LED secara serentak.

kaunter entiti ialah Port (clk: in STD_LOGIC; up_enable: in STD_LOGIC; down_enable: in STD_LOGIC; SEGMENTS: out STD_LOGIC_VECTOR (7 downto 0); DISP_EN: out STD_LOGIC_VECTOR (3 downto 0); led_clOG: out STD_LOGIC: out STD kaunter akhir; arsitektur Tingkah laku kaunter adalah komponen updown_counter adalah Port (present_state: out STD_LOGIC_VECTOR (3 downto 0); sebelumnya_state: di STD_LOGIC_VECTOR (3 downto 0); next_state: in STD_LOGIC_VECTOR (3 downto 0); clk: in STD_LOGIC; down_LOGIC; down_LOGIC; STD_LOGIC; up_enable: dalam STD_LOGIC); komponen akhir updown_counter; komponen counter_clkDiv adalah Port (clk: in std_logic; sclk: out std_logic); komponen akhir counter_clkDiv; komponen sseg_dec adalah Port (ALU_VAL: in std_logic_vector (7 downto 0); SIGN: in std_logic; VALID: in std_logic; CLK: in std_logic; DISP_EN: out std_logic_vector (3 downto 0); SEGMENTS: out std_logic; komponen akhir sseg_dec; komponen led_clkDiv adalah Port (present_state: in STD_LOGIC_VECTOR (3 downto 0); clk: in STD_LOGIC; led_clk: out STD_LOGIC); komponen akhir led_clkDiv; signal present_state: STD_LOGIC_VECTOR (3 ke bawah 0): = "0000"; signal next_state: STD_LOGIC_VECTOR (3 ke bawah 0): = "0000"; signal sebelumnya_state: STD_LOGIC_VECTOR (3 turun 0): = "0000"; isyarat Alu_Val: STD_LOGIC_VECTOR (7 turun 0); sclk isyarat: STD_LOGIC; mulakan Alu_Val (7 ke bawah 4) <= "0000"; Alu_Val (3 ke bawah 0) <= keadaan sekarang; next_state (0) <= tidak (present_state (0)); next_state (1) <= present_state (0) xor present_state (1); next_state (2) <= (present_state (0) dan present_state (1)) xor present_state (2); next_state (3) <= (present_state (0) dan present_state (1) dan present_state (2)) xor present_state (3); sebelumnya_state (0) <= tidak (present_state (0)); sebelumnya_state (1) <= present_state (0) xnor present_state (1); sebelumnya_state (2) <= (present_state (0) nor present_state (1)) xor present_state (2); sebelumnya_state (3) sclk, next_state => next_state, sebelumnya_state => sebelumnya_state, up_enable => up_enable, down_enable => down_enable, present_state => present_state); paparan: peta port sseg_dec (ALU_VAL => Alu_Val, SIGN => '0', VALID => '1', CLK => clk, DISP_EN => DISP_EN, SEGMENTS => SEGMENTS); led_div: peta port led_clkDiv (clk => clk, present_state => present_state, led_clk => led_clk); clk_div: peta port counter_clkDiv (clk => clk, sclk => sclk); Tingkah laku akhir;

Langkah 4: Menetapkan Kekangan dan Perhimpunan

Kekangan

Untuk menetapkan dan memprogram papan Basys 3 dengan betul, kita mesti terlebih dahulu menyiapkan fail kekangan kita yang dilampirkan pada langkah ini. Tetapan berikut telah disesuaikan:

Butang

- Diubah T18 menjadi "up_enable" (tingkatkan kecerahan)

- Diubah U17 menjadi "down_enable" (penurunan kecerahan)

Paparan 7 segmen

- W7, W6, U8, V8, U5, V5, U7, V7 mewakili setiap segmen satu paparan

- U2, U4, V4, W4 mewakili setiap anod yang dipaparkan (hanya 2 yang aktif kerana bilangan tertinggi kami adalah 15)

Ketua PMOD JC

JC7 adalah tempat kita menyambungkan salah satu wayar mentol LED, dan wayar lain mengarah ke GROUND

Setelah menetapkan semua ini, yang perlu anda lakukan adalah menjana aliran bit anda (dengan perisian apa pun yang anda gunakan iaitu Vivado), atur papan anda dan boom! Anda mempunyai papan kerja.

Catatan: Pemetaan pin boleh didapati di Lembaran Data Basys 3 di sini.

perhimpunan

Langkah 5: Menggunakan Suis Dimmer Anda

Sekiranya semuanya berjalan lancar, anda harus mempunyai sistem redup yang berfungsi sepenuhnya. Untuk meringkaskan, menekan butang atas akan meningkatkan kecerahan anda (sampai ke 15), dan menekan butang bawah akan menurunkan kecerahan anda (sampai ke 0). Semoga semuanya berjalan lancar untuk penglihatan anda sekarang yang santai!

Disyorkan:

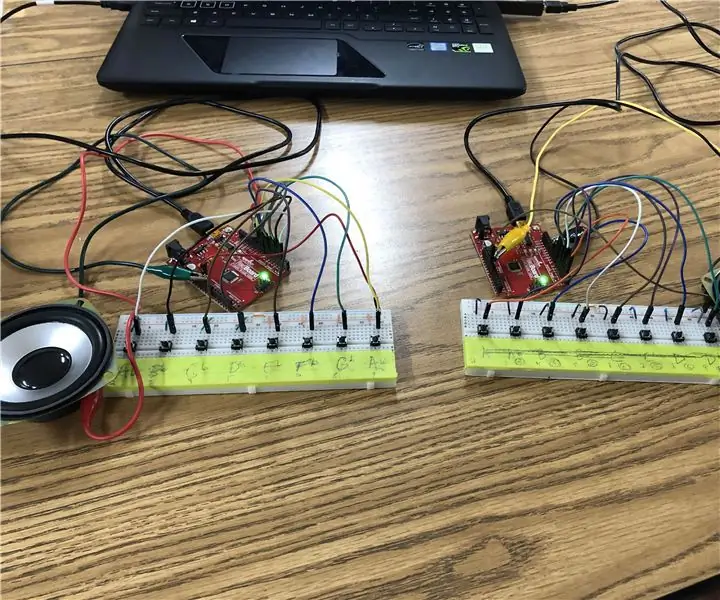

Papan Papan Arduino: 6 Langkah

Arduino Noteboard: Petunjuk ini akan menunjukkan cara membuat Arduino Noteboard. Papan ini dapat memainkan keseluruhan oktaf A-A dan flat mereka. Bahan: 18 wayar lelaki-lelaki16 butang18 wayar jumper mini4 pin lelaki4 Wayar Alligator2 Pembesar suara2 Papan Roti2 Arduin

Cara Menggunakan Papan Kompatibel Arduino WeMos D1 WiFi UNO ESP8266 IOT IDE dengan Menggunakan Blynk: 10 Langkah

Cara Menggunakan Arduino WeMos D1 WiFi UNO ESP8266 IOT IDE Compatible Board dengan Menggunakan Blynk: Arduino WeMos D1 WiFi UNO ESP8266 IOT IDE Compatible BoardKeterangan: WiFi ESP8266 Development Board WEMOS D1. WEMOS D1 adalah papan pengembangan WIFI berdasarkan ESP8266 12E. Fungsinya serupa dengan NODEMCU, kecuali perkakasan yang dibina

Lampu LED LED Dimmable LED: 5 Langkah (dengan Gambar)

Lampu LED LED Dimmable LED: Lampu banjir kadang-kadang cenderung berhenti berfungsi dari masa ke masa walaupun pada masa ini mereka menggunakan lampu LED. Ini mungkin disebabkan oleh banyak sebab seperti terlalu panas atau kesalahan pada pemandu LED atau kesalahan dalam proses pembuatan. Sebilangan besar dari kita akhirnya membuang prod

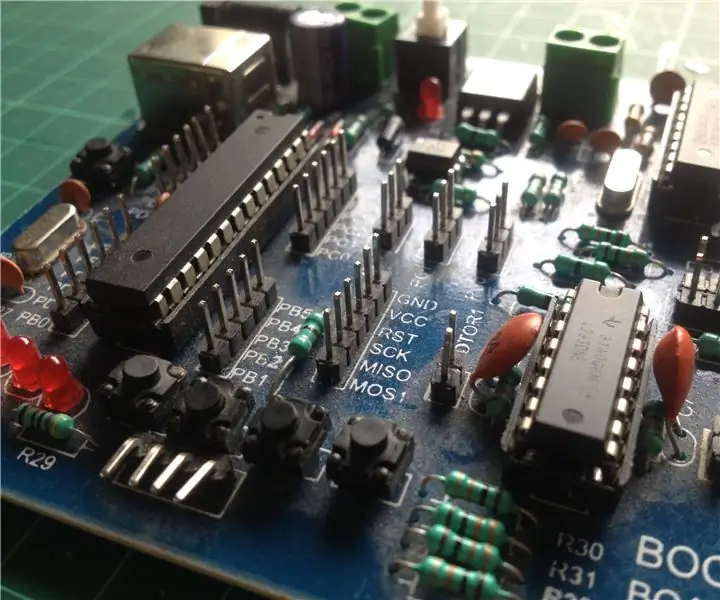

Cara Memprogram Papan AVR Menggunakan Papan Arduino: 6 Langkah

Cara Memprogram Papan AVR Menggunakan Papan Arduino: Adakah anda mempunyai papan mikrokontroler AVR yang terbaring? Adakah sukar untuk memprogramkannya? Baiklah, anda berada di tempat yang betul. Di sini, saya akan menunjukkan cara memprogram papan mikrokontroler Atmega8a menggunakan papan Arduino Uno sebagai pengaturcara. Jadi tanpa jarak

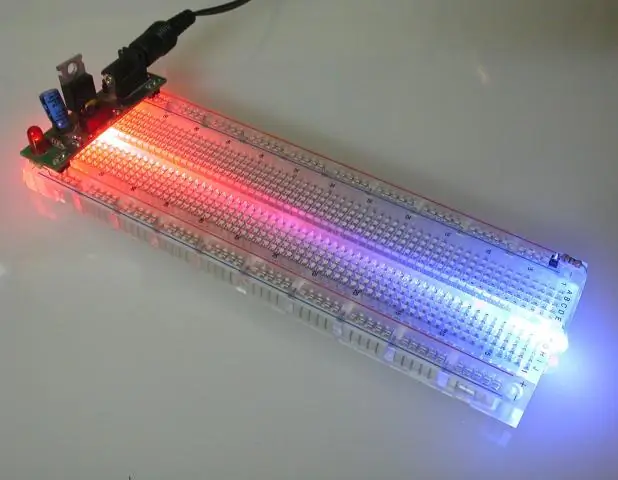

Melancarkan Papan Roti Anda (cara Menambah Petunjuk Daya LED ke Papan Roti Transparan Solarbotics): 7 Langkah

Bling Out Breadboard Anda (cara Menambah Indikator Daya LED ke Solarbotics Transparent Breadboard): Papan roti telus ini sama seperti papan roti elektronik lain, tetapi jelas! Jadi, apa yang boleh dilakukan dengan papan roti yang jelas? Saya rasa jawapan yang jelas adalah menambahkan LED kuasa