Isi kandungan:

- Langkah 1: Konfigurasikan Zynq Logicable Programmable for Transmitter

- Langkah 2: Konfigurasikan Logik yang Boleh Diprogram Zynq untuk Penerima

- Langkah 3: Sediakan Pemacu VDMA

- Langkah 4: Siapkan Rangkaian Nanorouter

- Langkah 5: Siapkan Sistem Pemprosesan Zynq untuk Penghantaran Data Melalui Ethernet

- Langkah 6: Siapkan Sistem Pemprosesan Zynq untuk Penerimaan Data Melalui Ethernet

- Langkah 7: Sambungkan Papan Zybo Anda ke Sumber HDMI dan Sink HDMI

- Langkah 8: Idea Alternatif untuk Penambahbaikan

- Langkah 9: Kebolehcapaian

- Pengarang John Day day@howwhatproduce.com.

- Public 2024-01-30 11:10.

- Diubah suai terakhir 2025-01-23 15:01.

Pernahkah anda berharap bahawa anda dapat menyambungkan TV anda ke PC atau komputer riba sebagai monitor luaran, tetapi tidak mahu menghalang semua tali sial itu? Sekiranya ya, tutorial ini hanya untuk anda! Walaupun terdapat beberapa produk yang mencapai tujuan ini, projek DIY jauh lebih memuaskan dan berpotensi lebih murah.

Konsep ini berbeza dengan produk seperti chromecast, kerana ia bertujuan untuk menggantikan kabel HDMI yang menghubungkan ke monitor dan bukannya menjadi peranti streaming.

Projek kami dibuat sebagai projek terakhir untuk kursus Sistem Operasi Masa Nyata di California State Polytechnic University, San Luis Obispo.

Matlamat projek ini adalah untuk menggunakan dua papan Digilent Zybo untuk bertindak sebagai antara muka komunikasi tanpa wayar antara peranti pemancar HDMI (PC, blu-ray, dll) ke peranti penerima HDMI (Monitor Desktop, Projektor, TV, dll.).

One Digilent Zybo akan disambungkan melalui HDMI ke peranti pemancar, dan yang lain akan disambungkan melalui HDMI ke peranti penerima.

Komunikasi tanpa wayar akan dibuat dengan menggunakan rangkaian kawasan setempat tanpa wayar yang dikhaskan untuk pemancar dan penerima, tanpa disalurkan melalui penghala rumah atau peranti lain yang lain. Modul wayarles yang digunakan untuk projek ini adalah tplink wr802n nanorouter, salah satunya beroperasi sebagai titik akses untuk mewujudkan rangkaian dan satu lagi untuk beroperasi sebagai pelanggan untuk menyambung ke rangkaian. Setiap nanorouter akan disambungkan melalui kabel ethernet ke salah satu papan Zybo. Apabila disambungkan ke penghala ini, peranti akan berkomunikasi melalui TCP seolah-olah mereka dihubungkan dengan kabel ethernet tunggal (yang bermaksud satu-satunya konfigurasi yang diperlukan untuk membuat sambungan adalah alamat IP klien).

Walaupun tujuan projek ini adalah untuk memudahkan aliran video 1080x720 @ 60Hz, ini tidak dapat dicapai kerana keterbatasan lebar jalur dalam rangkaian tanpa wayar dan kurangnya pemampatan video masa nyata untuk mengurangkan data yang diperlukan untuk dihantar. Sebagai gantinya, proyek ini berfungsi sebagai kerangka untuk pengembangan masa depan untuk mencapai tujuan ini, karena telah sangat membatasi batasan dalam frame rate untuk mengalirkan data HDMI dengan tepat seperti yang diharapkan.

Keperluan Projek:

Papan Pembangunan 2x Digilent Zybo (mesti mempunyai sekurang-kurangnya satu port HDMI)

2x kabel HDMI

2x kabel microusb (untuk menyambungkan Zybo ke PC untuk pembangunan)

2x tplink wr802n nanorouters (termasuk adtl. 2x microusb dan adapter power outlet dinding)

Kabel ethernet 2x

*** Catatan: Tutorial ini menganggap keakraban dengan rangkaian reka bentuk Vivado dan pengalaman membuat projek baru dan reka bentuk blok. ***

Langkah 1: Konfigurasikan Zynq Logicable Programmable for Transmitter

Pendekatan kami untuk mengembangkan logika pemancar yang dapat diprogram adalah dengan melakukan hantaran HDMI ke HDmi dari PC untuk memantau menggunakan dua blok Akses Langsung Memori Video (VDMA), satu untuk menulis dan satu untuk dibaca.

Kedua-duanya dipilih untuk mod bebas-3, bingkai-penyangga (0-1-2). Oleh kerana inti video dioptimumkan untuk 60 bingkai sesaat, ini bermakna VDMA akan menulis atau membaca ke bingkai baru setiap 16.67 ms dalam urutan ini: 0, 1, 2, 0, 1, 2, 0, 1, 2. Lokasi memori DDR untuk setiap bingkai berbeza untuk kedua VDMA kerana tidak lagi diselaraskan antara satu sama lain. Sebaliknya, pemasa perkakasan (TTC1), dikonfigurasi untuk 60 Hz, digunakan untuk menyegerakkan pergerakan data antara dua lokasi memori.

Gambar di atas menunjukkan 3 bingkai, dimensi dan jumlah memori masing-masing memerlukan (di sebelah kanan bingkai). Sekiranya kita menetapkan VDMA tulis ke lokasi memori ini, maka kita dapat menetapkan lokasi memori VDMA yang dibaca di luar set ini, katakan bermula dengan 0x0B000000. Setiap bingkai terdiri dari 1280 * 720 piksel dan setiap piksel terdiri dari 8 bit Merah, Hijau dan Biru untuk total 24 bit. Ini bermaksud bingkai terdiri daripada 1280 * 720 * 3 bait (2.76 MB).

Di dalam pemasa IRQ, yang dijelaskan dalam persediaan pemacu VDMA, akan menangani penyalinan data antara dua lokasi memori VMDA. VDMA memberikan penunjuk pada bingkai semasa yang sedang ditulis atau dibaca. Bingkai diwakili oleh kod kelabu tertentu, yang ditukar dalam perisian. Definisi kod kelabu untuk konfigurasi 3-penyangga bingkai boleh didapati di Panduan Produk AXI VDMA di lampiran C.

Ini membolehkan kita menyalin kandungan yang ditulis ke memori tanpa membaca dari bingkai yang sedang ditulis.

*** Perhatikan bahawa VDMA yang dibaca tidak digunakan ketika mengirim data di rangkaian tanpa wayar. Tujuannya hanyalah untuk mengesahkan operasi penyalinan memori yang betul dari VMDA tulis. VMDA yang dibaca harus dilumpuhkan. ***

Berikut adalah langkah-langkah untuk membuat Blok Reka Bentuk Pemancar:

- Semasa membuat projek baru, adalah idea yang baik untuk menetapkan chip atau papan untuk projek tersebut. Pautan ini menerangkan cara menambahkan fail papan baru ke direktori Vivado dan mengaitkan papan yang betul dengan projek anda. Ia akan sangat berguna ketika menambahkan blok Sistem Pemprosesan dan beralih dari perkakasan ke perisian (sisi SDK).

-

Tambahkan blok berikut:

- dvi2rgb

- Video masuk ke aliran Axi4

- Pengawal Masa

- axi4-stream untuk keluar

- rgb2dvi

- AXI VDMA x2

- AXI GPIO x2

- Penyihir Jam

- Pemalar

- Sistem Pemprosesan Zynq

- Semasa menambah Sistem Pemprosesan, klik "Jalankan Automasi Blok" dari bar berwarna hijau atas dan pastikan pilihan "Terapkan Preset Papan" dipilih. Biarkan semua perkara lalai.

- Gambar setiap tetingkap konfigurasi blok boleh didapati dalam gambar di atas. Sekiranya anda tidak melihat gambar untuk tetingkap tertentu, biarkan sebagai lalai.

-

Mula Mengkonfigurasi sistem Pemprosesan Zynq:

- Dalam Konfigurasi PS-PL AXI Tidak Selamat Aktifkan GP Master AXI, aktifkan M AXI GP0 Interface

- Dalam PS-PL Configuration HP Slave AXI Interface, aktifkan HP0 dan HP1

- Dalam MIO Configuration Pastikan ENET0 diaktifkan di bawah I / O Peripherals, kemudian Application Processor Unit, aktifkan Timer0

- Dalam Jam Fabric PL Configuration, aktifkan FCLK_CLK0 dan tetapkan ke 100 MHz.

- Klik Ok

- Sebelum mengklik "Jalankan Automasi Sambungan", pastikan untuk menyambungkan blok video seperti yang dilihat pada gambar reka bentuk blok TX di atas. Anda mahu menamakan semula pemalar menjadi VDD dan menetapkan nilai ke 1. Sambungkan blok video dengan sewajarnya.

- Jadikan pin HDMI TMDS dan pin data luaran pada blok rgb2dvi dan dvi2rgb

- Buat port input dan output untuk isyarat pengesanan palam panas (HPD) dan sambungkannya bersama, ini ditentukan dalam fail kekangan

-

Jam piksel dipulihkan dari TMDS_Clk_p, yang dibuat dalam fail kekangan. Ini akan menjadi 74,25 MHz sesuai dengan resolusi 720p. Penting untuk menyambungkan jam piksel (dari blok dvi2rgb) ke pin berikut:

- vid_io_in_clk (masuk ke blok aliran axi)

- vid_io_out_clk (axi stream untuk vid out block)

- clk (Pengawal Masa)

- PixelClk (rgb2dvi)

- *** Catatan: Pada masa ini, untuk mengaktifkan pemulihan jam piksel, penyambung HDMI rx dan tx mesti dipasang ke sumber / sink aktif. Salah satu cara untuk mengatasi ini ialah memisahkan blok rx dan tx video ke dalam domain jam yang berbeza (dengan kata lain, menghasilkan jam 74.25 MHz baru untuk dimasukkan ke blok tx). ***

- Seterusnya sediakan wizard jam supaya anda mempunyai input 100 MHz (sumber penyangga global) dan 3 jam output @ 50 MHz (jam AXI-Lite), 150 MHz (jam AXI4-Stream), 200 MHz (pin RefClk dvi2rgb).

- Sambungkan pin sistem pemprosesan FCLK_CLK0 ke input penyihir jam

- Pada ketika ini klik "Jalankan Automasi Sambungan" dari bar hijau di bahagian atas tetingkap reka bentuk. Sebaiknya lakukan ini untuk satu blok pada satu masa dan ikuti gambar reka bentuk blok TX di atas.

- Alat ini akan berusaha untuk menambahkan AXI Interconnect, yang berfungsi sebagai master / slave interconnect untuk blok yang menggunakan bas AXI-Lite (VDMA dan GPIO).

- Ia juga akan menambah AXI SmartConnect, yang bertindak sebagai penghubung utama / hamba untuk antara muka pemproses AXI4-Stream dan Prestasi Tinggi yang digunakan oleh VDMA (Stream ke Memory Map dan sebaliknya).

- Alat ini juga akan menambah Reset Sistem Prosesor. Pastikan ini hanya disambungkan ke blok yang berkaitan dengan VDMA, GPIO dan pemproses. Jangan sambungkannya ke mana-mana blok video (iaitu dvi2rgb, pengawal masa, vid ke aliran dll)

- Setelah automasi sambungan selesai, sahkan bahawa sambungannya sepadan dengan imej reka bentuk blok TX. Anda akan melihat blok ILA Sistem tambahan yang belum disebutkan. Ini hanya untuk penyahpepijatan dan tidak diperlukan buat masa ini. Ia menggunakan Reset Prosesor 150M, jadi itu juga tidak diperlukan. Di mana sahaja anda melihat "pepijat" hijau kecil di dalam bas, itu kerana ILA dan boleh diabaikan.

- Langkah terakhir adalah klik kanan pada reka bentuk blok di pohon sumber projek dan pilih "Buat HDL Wrapper." Sekiranya anda merancang untuk menambahkan logik ke pembungkus, itu akan ditimpa setiap kali ini dipilih.

- Lihat bahagian Persediaan Pemacu VDMA untuk perincian di bahagian SDK.

Jam dan Tetapan Semula

Saya dapati bahawa aspek terpenting dari mana-mana projek logik yang dapat diprogramkan adalah pertimbangan domain jam dan isyarat semula dengan teliti. Sekiranya mereka dikonfigurasikan dengan betul, anda mempunyai usaha yang baik untuk menjadikan reka bentuk anda berfungsi.

Jam Pixel dan Masa Dikunci

Untuk mengesahkan bahawa isyarat tertentu aktif, adalah idea yang baik untuk mengikat isyarat ini ke LED (jam, set semula, kunci dll). Dua isyarat yang saya anggap berguna untuk dilacak di papan pemancar adalah jam piksel dan isyarat "terkunci" pada blok AXI4-Streaming ke video out, yang memberitahu anda bahawa masa video telah diselaraskan dengan pengawal masa dan sumber video data. Saya telah menambahkan beberapa logik pada pembungkus blok reka bentuk yang mengesan jam piksel menggunakan isyarat PixelClkLocked pada blok dvi2rgb sebagai reset. Saya telah melampirkan fail sebagai hdmi_wrapper.v di sini. Fail kekangan juga dilampirkan di sini.

Langkah 2: Konfigurasikan Logik yang Boleh Diprogram Zynq untuk Penerima

Blok Logik yang Boleh Diprogram untuk penerima lebih mudah. Perbezaan utama, selain blok input HDMI yang hilang adalah ketiadaan jam piksel yang pulih. Untuk itu kita mesti menghasilkan sendiri dari penyihir jam. Reka bentuk ini harus dilakukan dalam projek yang terpisah dari pemancar. Untuk tujuan kami, projek penerima mengikuti papan Zybo 7Z-20 sementara Pemancar mengikuti papan Z7-10. FPGA di papan adalah berbeza jadi … berhati-hati.

Berikut adalah langkah-langkah untuk membuat Blok Reka Bentuk Penerima:

-

Tambahkan blok ip berikut ke reka bentuk anda:

- Pengawal Masa

- AXI4-Streaming ke Video Out

- RGB ke DVI

- AXI VDMA

- GPI AXI

- Sistem Pemprosesan

- Penyihir Jam

- Pemalar (VDD ditetapkan ke 1)

- Ikuti corak yang sama untuk mengkonfigurasi blok ini sebagai Pemancar. Gambar untuk perbezaan konfigurasi yang ketara telah disertakan di sini. Yang lain tetap sama dengan Pemancar.

- Konfigurasikan VDMA untuk reka bentuk ini sebagai saluran baca sahaja. Lumpuhkan saluran tulis.

-

Wizard jam harus dikonfigurasikan untuk output berikut:

- clk_out1: 75 MHz (jam piksel)

- clk_out2: 150 MHz (jam aliran)

- clk_out3: 50 MHz (jam axi-lite)

- Sambungkan blok video seperti yang ditunjukkan dalam gambar reka bentuk blok RX.

- Kemudian jalankan automasi sambungan, yang akan menambah blok AXI Interconnect, AXI SmartConnect dan System Reset dan cuba membuat sambungan yang sesuai. Pergi ke sini perlahan-lahan untuk memastikan ia tidak melakukan sambungan yang tidak diingini.

- Jadikan pin jam TMDS dan pin data diluar pada blok rgb2dvi

- Tidak memerlukan isyarat palam panas pada reka bentuk ini.

Langkah 3: Sediakan Pemacu VDMA

Penyediaan untuk blok yang berbeza yang dikonfigurasi melalui antara muka AXI-Lite paling baik dilakukan dengan menggunakan projek demo yang disertakan dengan BSP sebagai rujukan. Setelah mengeksport perkakasan reka bentuk dan melancarkan SDK dari Vivado, anda pasti ingin menambahkan pakej sokongan papan baru dan memasukkan pustaka lwip202 pada tetingkap tetapan BSP. Buka fail fail system.mss dari BSP dan anda akan melihat pemacu persisian hadir dari reka bentuk blok anda. Pilihan "Import Import" membolehkan anda mengimport projek demo yang menggunakan periferal ini dan dengan demikian menunjukkan kepada anda cara mengkonfigurasinya dalam perisian menggunakan pemacu Xilinx yang tersedia (lihat gambar yang dilampirkan).

Ini adalah kaedah yang digunakan untuk mengkonfigurasi VDMA, Timer & Interrupt, dan GPIO. Kod sumber untuk penghantaran dan penerimaan telah disertakan di sini. Perbezaannya hampir secara eksklusif dalam main.c.

*** CATATAN: Oleh kerana sistem ini tidak berfungsi sepenuhnya semasa menulis tutorial ini, kod sumber dalam bahagian ini tidak termasuk kod rangkaian tanpa wayar. Beberapa bug perlu ditangani sebagai hasil penggabungan projek transmisi / penerimaan inti video dengan projek penghantaran / penerimaan rangkaian. Oleh itu tutorial ini memperlakukan mereka secara berasingan buat masa ini. ***

Fungsi Pengendali Gangguan TX (IRQHandler)

Fungsi ini membaca kod kelabu yang disediakan oleh VDMA membaca dan menulis melalui blok GPIO. Kod kelabu ditukar menjadi perpuluhan dan digunakan untuk memilih lokasi memori asas bingkai bingkai semasa. Bingkai yang disalin adalah bingkai sebelumnya yang ditulis oleh VDMA (mis. Jika VDMA menulis ke bingkai 2, kami menyalin bingkai 1; jika menulis ke bingkai 0, kami membungkus dan membaca dari bingkai 2).

Fungsi hanya menangkap setiap bingkai ke-6 untuk mengurangkan kadar bingkai hingga 10 Hz daripada 60 Hz. Had atas rangkaian adalah 300 Mbps. Pada 10 bingkai sesaat, lebar jalur 221.2 Mbps diperlukan.

Mengomentari / tidak memberi komen dua baris dalam fungsi ini akan membolehkan pengguna menukar ke mod HDMI passthru untuk tujuan penyahpepijatan / ujian (kod tersebut dikomentari untuk menunjukkan garis yang sesuai). Pada masa ini, salinan bingkai ke lokasi memori yang digunakan oleh kod ethernet.

Fungsi Pengendali Ganggu RX (IRQHandler)

Fungsi ini sangat mirip dengan fungsi TX, tetapi menyalin dari 2 buffer FIFO yang digunakan oleh ethernet untuk menulis data masuk. Kod ethernet menunjukkan bingkai mana yang ditulis ke FIFO, data disalin dari bingkai yang berlawanan. Data disalin ke bingkai tepat di belakang yang dibaca oleh VDMA untuk mengelakkan robek.

Langkah 4: Siapkan Rangkaian Nanorouter

Untuk membuat rangkaian menggunakan nanorouters TPlink, hidupkan secara berasingan dan sambungkan ke SSID wifi lalai untuk peranti. Maklumat lebih lanjut mengenai tetapan konfigurasi untuk peranti ini boleh didapati melalui manual pengguna peranti.

Siapkan salah satu peranti sebagai titik akses, ini akan berfungsi sebagai sambungan utama untuk rangkaian. Pastikan untuk menamakan rangkaian dan perhatikan namanya, dan lumpuhkan DHCP (kami tidak mahu penghala mengkonfigurasi alamat IP secara dinamis, kami mahu papan pemancar dan penerima Zybo menetapkan alamat IP mereka sendiri agar mereka konsisten). Setelah mengkonfigurasi, pastikan peranti reboot dan mewujudkan rangkaian ini.

Siapkan peranti lain sebagai klien, dan pastikan ia menyambung ke SSID rangkaian yang anda siapkan dengan nanorouter pertama. Sekali lagi, pastikan bahawa DHCP dilumpuhkan untuk pelanggan.

Setelah pelanggan selesai dan reboot, ia harus menyambung ke nanorouter titik akses (jika tidak, kemungkinan ada masalah dalam konfigurasi salah satu peranti anda). Anda akan melihat bahawa lampu LED pada pelanggan akan padat setelah ia menyambung ke titik akses.

LED nanorouter titik akses kemungkinan akan terus berkelip pada ketika ini, tidak mengapa! Lampu berkelip bermaksud ia tidak disambungkan ke peranti lain dari port ethernetnya, dan setelah disambungkan ke Zybo yang dikonfigurasi, LED akan tetap padat menunjukkan sambungan rangkaian berjaya.

Sekarang setelah kami mengatur penyediaan nanorouters, kami mempunyai rangkaian tanpa wayar yang membolehkan kami berkomunikasi. Nota penting ialah kaedah konfigurasi kami untuk nanorouters (sebagai titik akses dan pelanggan) membolehkan kami berkomunikasi dari papan Zybo pemancar ke papan Zybo penerima seolah-olah keduanya dihubungkan dengan wayar ethernet tunggal. Ini menjadikan penyediaan rangkaian kami kurang sukar, kerana alternatifnya mungkin termasuk mengkonfigurasi papan Zybo untuk menyambung ke pelayan secara eksplisit bersama dengan koneksi yang dimaksudkan.

Setelah kedua-dua peranti disiapkan, nanorouters dikonfigurasi dan siap untuk dilaksanakan ke dalam rangkaian WIDI anda. Tidak ada pasangan khusus antara nanorouters dan papan Zybo, kerana titik akses atau pelanggan akan berfungsi sama ada untuk menghantar atau menerima peranti.

Langkah 5: Siapkan Sistem Pemprosesan Zynq untuk Penghantaran Data Melalui Ethernet

Untuk menghantar data HDMI dari satu papan Zybo ke papan yang lain, kita mesti memasukkan protokol Ethernet dengan pemacu VDMA kami. Tujuan kami di sini adalah untuk mengalirkan bingkai video individu melalui periferal Ethernet dalam sistem pemprosesan, pada kadar yang ditetapkan yang selaras dengan lebar jalur rangkaian kami. Untuk projek kami, kami menggunakan TCP yang disediakan oleh API LwIP bare-metal. Oleh kerana kedua-dua anggota projek ini relatif tidak berpengalaman dengan utiliti rangkaian, pilihan ini dibuat tanpa menyedari sepenuhnya implikasi dan kekangan yang terlibat dengan TCP. Masalah utama pelaksanaan ini adalah lebar jalur yang terhad dan fakta bahawa ia sebenarnya tidak dirancang untuk tujuan mengukus data dalam jumlah yang tinggi. Penyelesaian alternatif untuk menggantikan TCP dan memperbaikinya dalam projek ini akan dibincangkan kemudian.

Penerangan ringkas mengenai TCP dengan LwIP: Data dikirim melalui rangkaian dalam paket ukuran tcp_mss (ukuran segmen maksimum TCP), yang umumnya 1460 bait. Memanggil tcp_write akan mengambil beberapa data yang dirujuk oleh penunjuk dan mengkonfigurasi pbuf (paket penyangga) untuk menyimpan data dan memberikan struktur untuk operasi TCP. Jumlah maksimum data yang dapat diatur dalam satu waktu ditetapkan sebagai tcp_snd_buf (ruang penyangga pengirim TCP). Oleh kerana parameter ini adalah nombor 16 bit, kita terhad kepada ukuran buffer kirim 59695 byte (terdapat beberapa padding yang diperlukan dalam buffer kirim). Setelah data diantrekan, tcp_output dipanggil untuk mulai mengirimkan data. Sebelum menghantar segmen data seterusnya, adalah mustahak semua paket sebelumnya berjaya dihantar. Proses ini dilakukan dengan menggunakan fungsi recv_callback, kerana ini adalah fungsi yang dipanggil ketika pengakuan dilihat dari penerima.

Menggunakan contoh projek dalam Vivado SDK sangat membantu untuk belajar bagaimana operasi LwIP TCP, dan merupakan titik permulaan yang baik untuk memulakan projek baru.

Prosedur untuk peranti pemancar WiDi adalah seperti berikut:

- Memulakan rangkaian TCP menggunakan panggilan fungsi pemacu LWIP bare-metal.

- Tentukan fungsi panggilan balik yang diperlukan untuk operasi rangkaian.

- Sambungkan ke penerima WiDi dengan menyambung ke alamat IP dan portnya (konfigurasi kami: Penerima IP adalah 192.168.0.9, sambungkan ke port 7).

- Apabila pemasa pemacu VDMA tamat, masukkan TX ISR.

- Tentukan penyangga bingkai semasa untuk diakses berdasarkan kod kelabu VDMA

- Beratur segmen pertama data dalam penyangga hantaran TCP

- Keluarkan data, dan kemas kini pemboleh ubah tempatan untuk mengawasi berapa banyak data yang telah dikirim dari bingkai saat ini.

- Setelah mencapai panggilan balik yang diterima (fungsi panggilan dibuat setelah pemancar mendapat pengakuan pengambilan data), barisan segmen data berikutnya.

- Ulangi langkah 7 & 8 sehingga keseluruhan bingkai telah dihantar.

- Kembali ke keadaan siaga untuk menunggu pemasa seterusnya mengganggu untuk menunjukkan bingkai baru sudah siap (Kembali ke langkah 4).

Pastikan untuk menetapkan tetapan LwIP pakej sokongan papan seperti yang ditunjukkan pada gambar di atas. Semua nilai adalah lalai kecuali tcp_snd_buf, tcp_pueue_ooseq, mem_size, memp_n_tcp_seg. Perhatikan juga bahawa debugging terperinci dapat dicapai dengan mengubah parameter BSP untuk kumpulan debug_options.

Langkah 6: Siapkan Sistem Pemprosesan Zynq untuk Penerimaan Data Melalui Ethernet

Papan pengembangan Zybo yang akan berfungsi sebagai penerima tanpa wayar akan beroperasi sama dengan peranti pemancar. Tetapan pakej sokongan papan untuk LwIP akan sama dengan yang ada pada langkah sebelumnya.

Peranti akan mengambil paket yang berisi segmen bingkai video dari nanorouter, dan akan menyalin data bingkai video ke ruang penyangga tiga bingkai untuk VDMA penerima. Untuk mengelakkan menimpa data apa pun, buffer data berganda (kami akan sebut sebagai buffer rangkaian) digunakan ketika mengumpulkan data dari nanorouter, sehingga lalu lintas jaringan dapat terus streaming sementara bingkai video penuh sebelumnya disalin ke Penampan VDMA.

Prosedur untuk peranti penerima WiDi memerlukan dua tugas, salah satunya adalah menerima data ethernet, dan yang lainnya adalah menyalin bingkai video dari penyangga jaringan ke penyangga bingkai tiga VDMA.

Tugas penerimaan Ethernet:

- Memulakan rangkaian TCP menggunakan panggilan fungsi pemacu LWIP bare-metal (persediaan dengan alamat IP yang akan disambungkan oleh pemancar, 192.168.0.9 di kami)

- Tentukan fungsi panggilan balik yang diperlukan untuk operasi rangkaian.

- Setelah menerima paket ethernet, salin data paket ke penyangga rangkaian semasa, tingkatkan data terkumpul semasa.

- Sekiranya paket mengisi penyangga kerangka rangkaian, teruskan ke langkah 5 & 6. Jika tidak, kembali ke langkah 3 dari tugas ini.

- memberi isyarat bahawa tugas penyangga bingkai tiga VDMA harus disalin dari penyangga rangkaian yang baru selesai.

- Beralih ke penyangga rangkaian yang lain dan terus mengumpulkan data melalui ethernet.

- Lengah sehingga paket ethernet baru diterima (langkah 3).

Salin buffer rangkaian ke buffer triple frame VDMA:

- Apabila pemasa pemacu VDMA tamat, masukkan RX ISR.

- Tentukan bingkai penyangga semasa untuk diakses berdasarkan kod kelabu VDMA.

- Tentukan penyangga rangkaian mana yang akan disalin ke penyangga VDMA, dan salin data tersebut

Langkah 7: Sambungkan Papan Zybo Anda ke Sumber HDMI dan Sink HDMI

Sekarang sambungkan kabel HDMI untuk penerima dan pemancar, atur program FPGA dan jalankan sistem pemprosesan. Kadar bingkai mungkin akan sangat perlahan, kerana overhead yang besar dalam operasi LwIP dan lebar jalur yang terhad. Sekiranya ada masalah, sambung melalui UART dan cuba kenal pasti sebarang amaran atau kesalahan.

Langkah 8: Idea Alternatif untuk Penambahbaikan

Masalah besar untuk projek ini adalah jumlah data yang diperlukan untuk menghantar wifi. Ini sudah dijangkakan, namun kami meremehkan kesan yang akan terjadi dan mengakibatkan lebih banyak gambar meletup di layar dan bukannya umpan video. Terdapat beberapa cara untuk memperbaiki projek ini:

- Pemampatan video masa nyata. Memampatkan bingkai video feed masuk dengan bingkai akan sangat mengurangi jumlah data yang diperlukan untuk dikirim melalui jaringan. Sebaiknya ini dilakukan dalam perkakasan (yang bukan tugas yang mudah), atau boleh dilakukan dalam perisian dengan menggunakan teras ARM yang lain untuk menjalankan algoritma pemampatan (ini memerlukan analisis lebih lanjut untuk memastikan waktunya berjalan lancar). Terdapat beberapa komponen pemampatan video masa nyata sumber terbuka yang kami dapati di web, tetapi sebahagian besarnya adalah IP.

- Menerapkan aliran Ethernet dalam perkakasan, bukannya perisian. Terdapat banyak overhead karena kekurangan ruang yang tersedia untuk mengantri data keluar dalam pemancar, karena keterbatasan pada ukuran segmen. Proses yang lebih cekap adalah menggunakan AXI Ethernet IP dengan penyangga FIFO atau DMA untuk memasukkan data ke dalamnya. Ini akan mengurangkan bagasi tambahan dari LwIP TCP dan memungkinkan lebih banyak aliran data.

Langkah 9: Kebolehcapaian

Produk yang dihasilkan dari projek WiDi ini mestilah sepasang peranti padat yang padat yang boleh disambungkan oleh pengguna ke mana-mana sumber HDMI dan kemudian memasukkan suapan video ke paparan dengan kemampuan HDMI secara wayarles. Peranti akan menampilkan SoC Zynq-7000 yang terdapat di papan rujukan Zybo dan menggabungkan perkakasan rangkaian yang terdapat di router nano TP-Link. Sebaik-baiknya, pengguna dapat mengawal modul pemancar dari lokasi diskrit dalam sistem operasi sasaran, dengan sedikit keperluan kemampuan teknikal yang signifikan.

Keselamatan dan Kesambungan

Peranti juga harus menggabungkan Transport Layer Security (TLS) dan mempunyai kemampuan menyambung automatik yang terhad, baik untuk tujuan privasi. Niat para pereka untuk menjadikan hubungan dengan paparan melalui antara muka tanpa wayar merupakan tindakan yang disengajakan bagi pihak pengguna untuk mengelakkan penyiaran bahan sensitif secara tidak sengaja.

Status Semasa

Sehingga ke tahap ini, keadaan projek ini masih banyak dijalankan. Agar pengguna titik akhir semasa mendapat manfaat daripada tutorial ini, dia mesti mempunyai pemahaman teknikal yang kuat mengenai reka bentuk sistem tertanam dan semestinya mempunyai keakraban dengan perkakasan yang dapat diprogramkan dan perisian terbenam yang bekerjasama.

Data yang dikirim melalui jaringan tidak dienkripsi pada saat ini dan dianggap sebagai transmisi mentah paket TCP / IP.

Projek teras video berjaya diuji untuk penghantaran dan penerimaan. Sebaliknya, sambungan tanpa wayar antara dua papan zybo terjalin dan data bingkai ujian berjaya dihantar. Namun, masih perlu menggabungkan kod rangkaian ke setiap projek teras video dan menguji penghantaran bingkai video sebenar.

Disyorkan:

Papan Pembangunan DIY ESP32 - ESPer: 5 Langkah (dengan Gambar)

Papan Pembangunan DIY ESP32 - ESPer: Baru-baru ini saya telah membaca banyak IoT (Internet of Things) dan percayalah, saya tidak sabar untuk menguji salah satu peranti hebat ini, dengan kemampuan untuk menyambung ke internet, saya sendiri dan mula bekerja. Nasib baik peluang

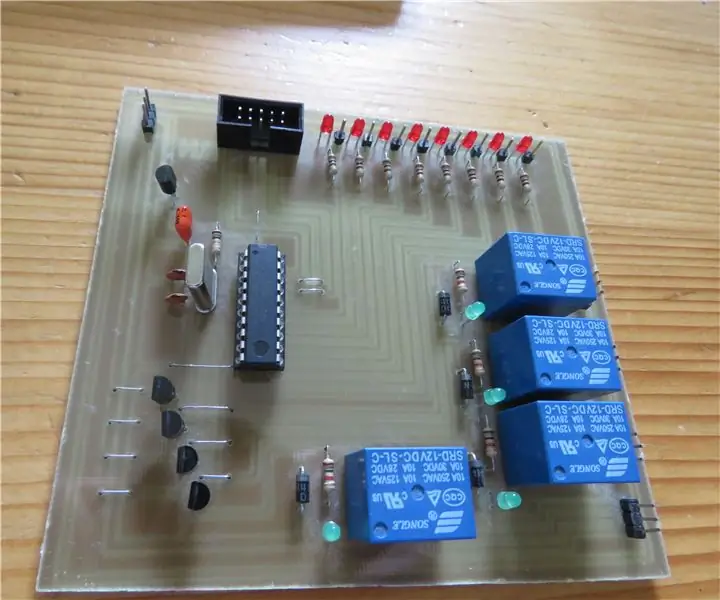

Buat Papan Pembangunan Anda Sendiri Dengan Pengawal Mikro: 3 Langkah (dengan Gambar)

Buat Papan Pembangunan Anda Sendiri Dengan Mikrokontroler: Adakah anda pernah mahu membuat papan pengembangan anda sendiri dengan mikrokontroler dan anda tidak tahu bagaimana. Dalam arahan ini saya akan menunjukkan kepada anda bagaimana membuatnya. Yang anda perlukan adalah pengetahuan dalam elektronik, merancang litar dan pengaturcaraan. Sekiranya anda mempunyai usaha

Merancang Papan Pembangunan Mikrokontroler: 14 Langkah (dengan Gambar)

Merancang Lembaga Pengembangan Mikrokontroler: Adakah anda pembuat, penggemar hobi, atau penggodam berminat untuk melangkah dari projek perfboard, IC DIP dan PCB buatan sendiri ke PCB pelbagai lapisan yang dibuat oleh rumah papan dan pembungkusan SMD yang siap untuk pengeluaran besar-besaran? Maka arahan ini untuk anda! Gui ini

Quadcopter Menggunakan Papan Zybo Zynq-7000: 5 Langkah

Quadcopter Menggunakan Papan Zybo Zynq-7000: Sebelum kita memulakan, berikut adalah beberapa perkara yang anda mahukan untuk projek ini: Senarai Bahagian1x Digilent Zybo Zynq-7000 board 1x Quadcopter Frame mampu memasang Zybo (fail Adobe Illustrator untuk lasercutting terpasang) 4x Turnigy D3530 / 14 1100KV Motor Tanpa Berus 4x

Bina Papan Pembangunan Anda Sendiri: 8 Langkah (dengan Gambar)

Bina Lembaga Pembangunan Anda Sendiri: Instruksional ini akan menunjukkan kepada anda bagaimana membina papan pengembangan anda sendiri dari awal! Kaedah ini mudah dan tidak memerlukan alat canggih, anda bahkan boleh melakukannya di meja dapur anda. Ini juga memberi pemahaman yang lebih baik tentang bagaimana Ardruinos dan