Isi kandungan:

- Pengarang John Day day@howwhatproduce.com.

- Public 2024-01-30 11:07.

- Diubah suai terakhir 2025-01-23 15:00.

Oleh AmCoderhttps://www.linkedin.com/in/mituFollow Lagi oleh pengarang:

Tentang: Mitu Raj - Just a Hobbyst and Learner - Chip Designer - Pembangun Perisian - Penggemar Fizik dan Matematik Lebih banyak Mengenai AmCoder »

## Ini adalah pautan yang paling banyak diklik dan popular di Google untuk pelaksanaan VHDL ALGORITHM CORDIC untuk menghasilkan gelombang sinus dan kosinus ## Pada masa ini, terdapat banyak algoritma cekap perkakasan, tetapi ini tidak terkenal kerana dominasi sistem perisian di bertahun-tahun. CORDIC adalah algoritma yang tidak lain hanyalah satu set logik shift dan add yang digunakan untuk mengira pelbagai fungsi termasuk fungsi trigonometri, hiperbolik, linear dan logaritmik tertentu. Ini adalah algoritma yang digunakan dalam kalkulator dll. Oleh itu, dengan hanya menggunakan pemindah dan penambah sederhana, kita dapat merancang perkakasan dengan kerumitan yang kurang tetapi kekuatan DSP menggunakan algoritma kordik. Oleh itu ia boleh dirancang sebagai reka bentuk RTL yang kosong dalam VHDL atau Verilog tanpa menggunakan unit titik apungan khusus atau IP matematik yang kompleks.

Langkah 1: VHDL dan Modelsim

Di sini algoritma kordik dilaksanakan menggunakan VHDL untuk menghasilkan gelombang sinus dan gelombang cose. Ia dapat mengeluarkan sinus dan kosinus sudut input dengan tepat. Kod ini boleh disintesis pada FPGA. Modelsim digunakan untuk mensimulasikan reka bentuk dan bangku ujian.

Langkah 2: Kod VHDL untuk Reka Bentuk dan Bangku Uji

Teknik penskalaan binari digunakan untuk mewakili nombor titik terapung.

Sila pergi melalui dokumen yang dilampirkan sebelum anda membuat kod.

Pergi melalui Simulasi cordic_v4.vhd - Reka Bentuknya - Input adalah sudut dalam 32 bit + tanda bit; ia dapat memproses sebarang sudut dari 0 hingga +/- 360 darjah dengan ketepatan input 0,000000000233 darjah. Semasa memberi input -> MSB adalah bit tanda dan selebihnya 32 bit mewakili magnitud. - Output reka bentuk adalah nilai sinus dan kosnya dalam 16 bit + bit tanda.ie; dengan ketepatan 0.00001526. Harap maklum bahawa output ditunjukkan dalam bentuk pujian 2 jika nilai sinus atau kos masing-masing adalah negatif. Simulasi testb.vhd - Bangku Uji Untuk Reka Bentuk (1) Sudut input dan tetapan semula tarik = '0'. Setelah dua langkah simulasi tarik semula ke '1' dan "jalankan semua". (2) Di tetingkap simulasi tetapkan sinaran sinaran sin dan kos sebagai perpuluhan dan format> Analog (automatik). (3) Zum keluar untuk melihat bentuk gelombang dengan betul.

Langkah 3: Fail Dilampirkan

(1) cordic_v4.vhd - Reka bentuk. (2) testb.vhd - Bangku ujian untuk reka bentuk.

(3) Dokumen mengenai cara memaksa input sudut dan menukar hasil binari.

Kemas kini: FILE INI DIBAWA DAN TIDAK DISEDIAKAN LAGI. SILA GUNAKAN FILES DARI LANGKAH SETERUSNYA

Langkah 4: Teras IP Mini-Kordik - 16 Bit

Batasan pelaksanaan di atas adalah- lambat, frekuensi jam operasi lebih rendah kerana melakukan pengiraan dalam satu pusingan jam. Inti IP Mini-Kordik - 16 Bit

- Laluan kritikal diedarkan ke beberapa kitaran untuk meningkatkan prestasi.- Lebih pantas - Reka bentuk terbukti FPGA disintesis hingga jam 100 Mhz.- Lebih banyak kawasan dioptimumkan dalam HDL, perkakasan yang lebih rendah.- Isyarat Status Beban dan Selesai ditambahkan.- Satu-satunya kelemahan adalah resolusi yang lebih rendah berbanding dengan sebelumnya. Testbench:

automatik sepenuhnya dari input sudut 0 hingga 360 darjah

Fail yang dilampirkan: 1) fail vhdl utama kordik mini2) bangku ujian mini kordik3) manual Teras IP Kord Mini4) Dokumen mengenai cara memaksa sudut dan menukar hasil

Untuk sebarang pertanyaan, sila hubungi saya:

Mitu Raj

ikuti saya:

mel: iammituraj@gmail.com

### Jumlah muat turun: 325 hingga 01-05-2021 ###

### Kod diedit terakhir: 07-2020 Julai ###

Disyorkan:

Robot Pengimbangan Diri - Algoritma Kawalan PID: 3 Langkah

Self Balancing Robot - PID Control Algorithm: Projek ini dibuat kerana saya berminat untuk mempelajari lebih lanjut mengenai Control Algorithms dan bagaimana melaksanakan loop PID berfungsi dengan berkesan. Projek ini masih dalam fasa pembangunan kerana modul Bluetooth belum ditambah yang akan

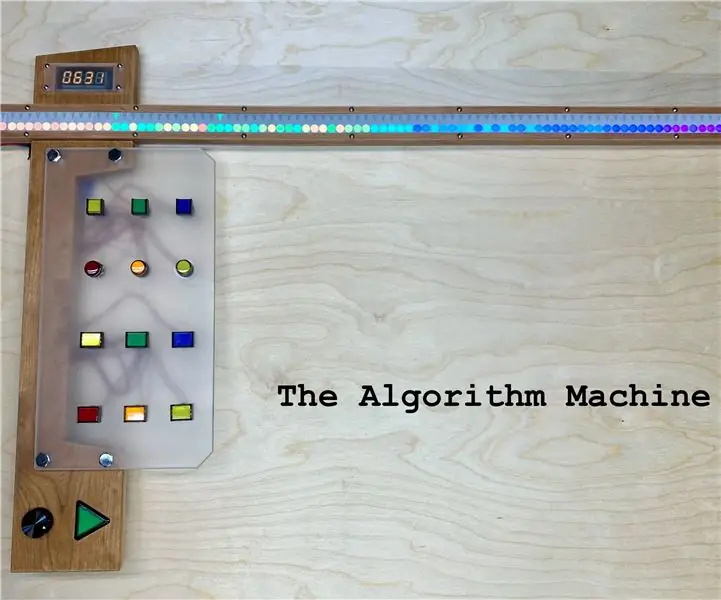

Mesin Algoritma: 13 Langkah (dengan Gambar)

Mesin Algoritma: Saya telah mengajar sains komputer di peringkat kuliah selama 15 tahun, dan walaupun kepakaran saya lebih kepada aspek pengaturcaraan, saya masih menghabiskan banyak masa untuk merangkumi algoritma standard untuk mencari dan menyusun. Dari sudut pengajaran

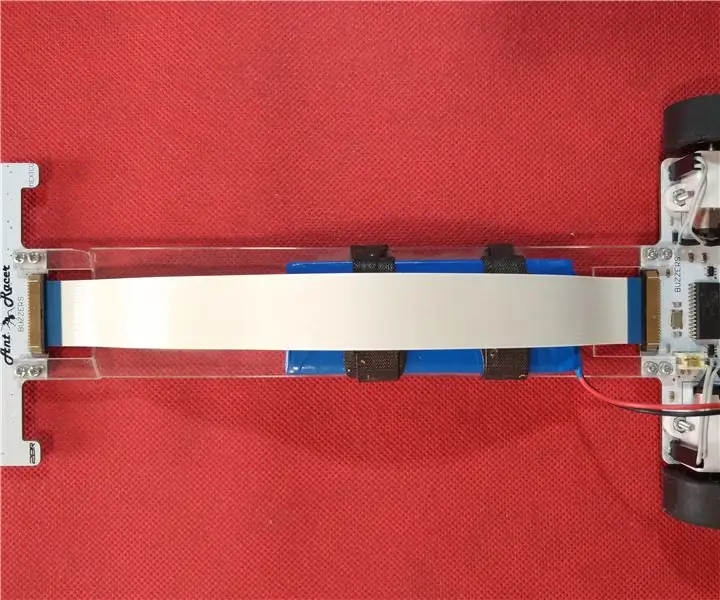

Line Follower Robot untuk Algoritma Kawalan Pengajaran: 3 Langkah

Line Follower Robot for Teaching Control Algorithms: Saya merancang robot pengikut garis ini beberapa tahun yang lalu ketika saya menjadi guru robotik. Objektif untuk projek ini adalah untuk mengajar pelajar saya bagaimana membuat kod baris robot berikut untuk pertandingan dan juga membandingkan antara kawalan If / Else dan PID. Dan tidak

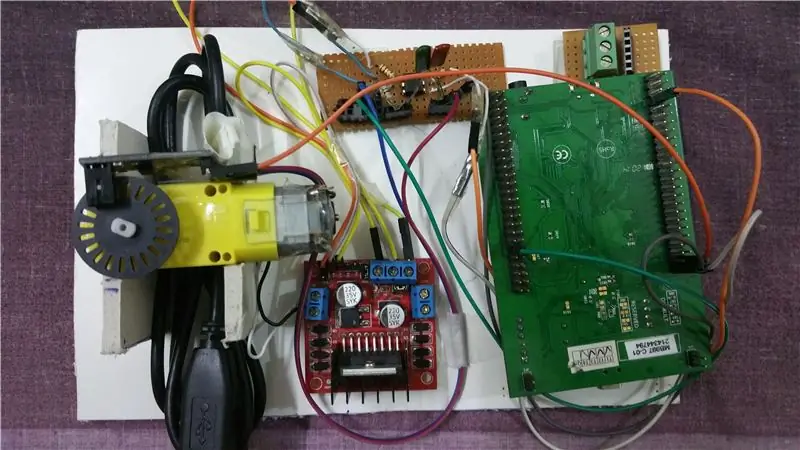

Robot Mengimbangkan Diri Menggunakan Algoritma PID (STM MC): 9 Langkah

Robot Pengimbangan Diri Menggunakan Algoritma PID (STM MC): Baru-baru ini banyak kerja yang dilakukan dalam mengimbangkan objek. Konsep pengimbangan diri bermula dengan pengimbangan bandul terbalik. Konsep ini juga merangkumi reka bentuk kapal terbang. Dalam projek ini, kami telah merancang mod kecil

Kawalan Kelajuan Motor DC Menggunakan Algoritma PID (STM32F4): 8 Langkah (dengan Gambar)

Kawalan Kelajuan Motor DC Menggunakan Algoritma PID (STM32F4): halo semua, Ini tahir ul haq dengan projek lain. Kali ini STM32F407 sebagai MC. Ini adalah akhir projek semester pertengahan. Harap anda menyukainya. Ia memerlukan banyak konsep dan teori sehingga kita membincangkannya terlebih dahulu. Dengan munculnya komputer dan