Isi kandungan:

- Pengarang John Day day@howwhatproduce.com.

- Public 2024-01-30 11:08.

- Diubah suai terakhir 2025-01-23 15:01.

Matlamat kami dengan projek ini adalah untuk mencipta sesuatu yang dapat menjimatkan sumber tenaga dan kewangan masyarakat. Lampu jalan yang diaktifkan bergerak akan melakukan kedua-dua perkara ini. Tenaga di seluruh negara disia-siakan di lampu jalan yang menerangi jalan-jalan yang kosong. Sistem lampu jalan kami memastikan bahawa lampu hanya menyala apabila diperlukan, menjimatkan wang masyarakat yang tidak terhitung jumlahnya. Dengan menggunakan sensor gerakan, sistem akan menyalakan lampu hanya apabila kereta ada. Juga untuk keselamatan pejalan kaki, kami menggunakan butang ganti yang menyalakan semua lampu di jalan. Langkah-langkah berikut akan memandu anda bagaimana kami merancang dan membina model projek kami yang diperkecil menggunakan Vivado dan papan Basys 3.

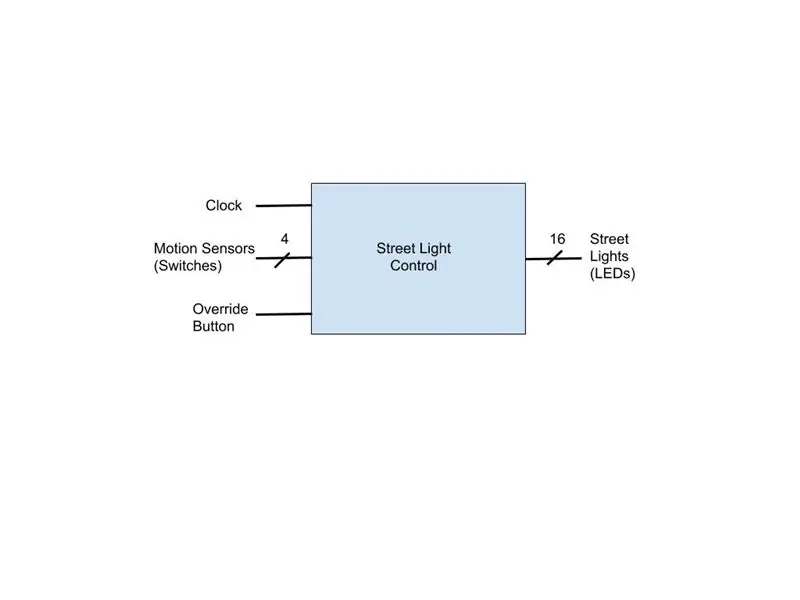

Langkah 1: Kotak Hitam Sistem

Kami memulakan projek ini dengan melukis gambar rajah kotak hitam sederhana. Gambar rajah kotak hitam menunjukkan input dan output yang diperlukan oleh sistem kita untuk menyelesaikan semua proses yang diperlukan. Kami berusaha memastikan reka bentuk kami sesederhana dan asas mungkin. Tiga input sistem kami merangkumi bas sensor gerakan (4 untuk model skala bawah kami), butang penimpaan pejalan kaki, dan input jam. Di sisi lain output tunggal kami adalah bas lampu LED yang mewakili lampu jalan kami. Untuk model ini, kami menggunakan senario 16 lampu jalan kerana itu adalah jumlah maksimum keluaran LED terpasang di papan Basys 3. Akhirnya, dengan menggunakan rajah ini, kami dapat membuat projek, sumber, dan fail kekangan Vivado kami dengan input dan output yang sesuai.

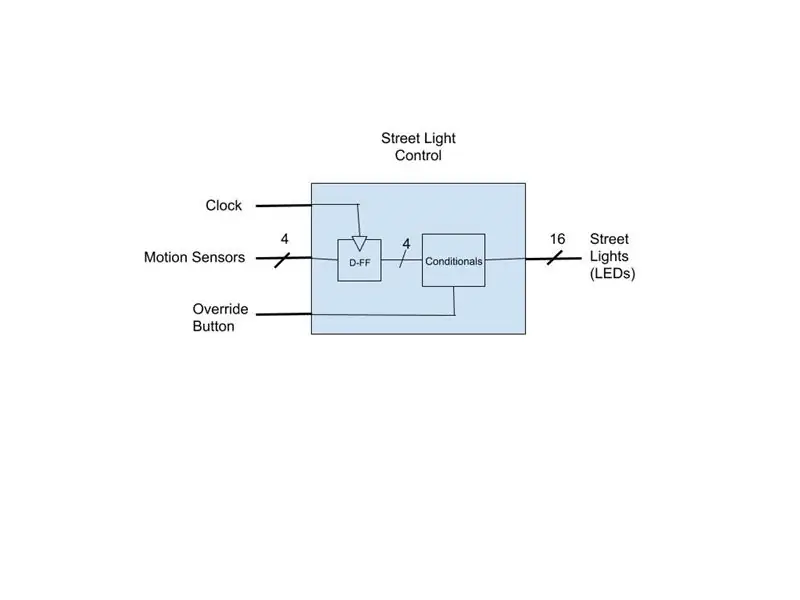

Langkah 2: Komponen

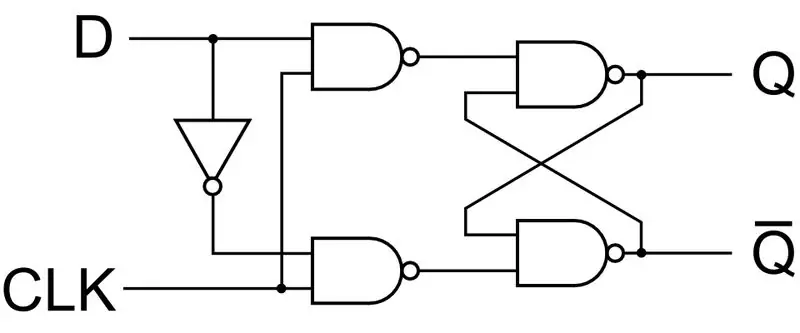

Dalam langkah ini kita menyelami lebih mendalam memeriksa komponen-komponen yang membentuk rajah kotak hitam kita. Komponen pertama kami adalah fail sumber VHDL yang mengandungi D flip-flop. Flip-flop D hanya mengambil apa sahaja isyarat yang dimasukkan ke mereka dari sensor pada tepi jam yang semakin meningkat, dan memasukkan data tersebut sehingga naik ke seterusnya. Ini menjadikan sensor gerakan sensitif kita tidak menyebabkan LED output dari "kelipan". Kami juga meletakkan satu flip-flop D pada isyarat input butang untuk menyalakan LED selama kira-kira 5-7 saat setelah butang ditekan. Kami juga menjalankan ini melalui pembahagi jam.

entiti clk_div2 adalah Port (clk: in std_logic; sclk: out std_logic); tamat clk_div2;

seni bina my_clk_div dari clk_div2 adalah

jumlah maksimum_kata: bilangan bulat: = (300000000); isyarat tmp_clk: std_logic: = '0'; mulakan my_div: proses (clk, tmp_clk) pemboleh ubah div_cnt: integer: = 0; mulakan jika (meningkat_kebaikan (clk)) maka jika (div_cnt = MAX_COUNT) maka tmp_clk <= bukan tmp_clk; div_cnt: = 0; lain div_cnt: = div_cnt + 1; tamat sekiranya; tamat sekiranya; sclk <= tmp_clk; proses akhir my_div; tamatkan my_clk_div;

Komponen terakhir kami dalam rajah ini adalah fail sumber VHDL tingkah laku yang mengandungi syarat untuk output berdasarkan konfigurasi isyarat input.

Langkah 3: D Flip-Flops

Keempat flip-flop yang terpasang pada isyarat input sangat penting untuk fungsi sistem kami. Seperti yang dinyatakan sebelumnya, dengan sensor gerakan sensitif dan butang ganti, flip-flop menggunakan selak untuk hanya mengeluarkan isyarat input kami di tepi jam yang semakin meningkat. Logik berurutan ini bermaksud lampu jalan kami dapat terus menyala untuk jangka masa yang ditetapkan setelah dipicu oleh gerakan pantas. Pengekodan untuk D-Flip Flop cukup mudah:

beginprocess (CLK) bermula jika meningkat_kebaikan (CLK) maka Q <= D; tamat sekiranya; proses akhir;

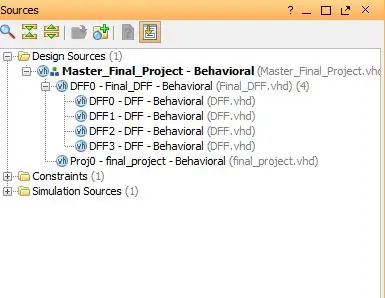

Seluruh perkara boleh disusun menjadi satu penyataan jika. Sebaik sahaja kami mempunyai karya ini, kami membuat fail sumber VHDL struktur yang mengandungi keempat-empat flip-flop kami yang diperlukan:

mulakan DFF0: peta port DFF (CLK => CLK, D => D (0), Q => Q (0)); DFF1: Peta port DFF (CLK => CLK, D => D (1), Q => Q (1)); DFF2: Peta port DFF (CLK => CLK, D => D (2), Q => Q (2)); DFF3: Peta port DFF (CLK => CLK, D => D (3), Q => Q (3));

Tingkah laku akhir;

Ini membantu mengekalkan fail struktur utama kami di mana kami mengumpulkan semua komponen sistem dengan lebih bersih dan teratur.

Langkah 4: Bersyarat

Untuk memastikan kod kami tetap padat dan cekap, kami menulis semua syarat dalam satu penyataan kes. Untuk model yang diperkecil, kami mempunyai 16 kemungkinan konfigurasi output LED kerana setiap sensor gerakan bertanggungjawab untuk sekumpulan 4 LED.:

kes NMS ialah apabila "1111" => LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED = = 1111111111111111 "; kes akhir;

Langkah 5: Kekangan

Untuk menyatakan input dan output dengan betul menggunakan Vivado, anda mesti menerapkan fail kekangan yang menyatakan semua port, butang, LED dan jam yang digunakan.

set_property PACKAGE_PIN W5 [get_ports CLK] set_property IOSTANDARD LVCMOS33 [get_ports CLK]

set_property PACKAGE_PIN U16 [get_ports {LED [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [0]}] set_property PACKAGE_PIN E19 [get_ports {LED [1]}] set_property IOSTANDARD LVCMOS33 [get_ports] LED [1_Perusahaan] LED [1] U19 [get_ports {LED [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [2]}] set_property PACKAGE_PIN V19 [get_ports {LED [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [3]}] set_property PACKAGE [set_property W18] get_ports {LED [4]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [4]}] set_property PACKAGE_PIN U15 [get_ports {LED [5]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [5]}] set_property PACKAGE_PIN LED [6]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [6]}] set_property PACKAGE_PIN V14 [get_ports {LED [7]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [7]}] set_property PACKAGE_PIN V13 [get 8]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [8]}] set_property PACKAGE_PIN V3 [get_ports {LED [9]}] set_property IO STANDARD LVCMOS33 [get_ports {LED [9]}] set_property PACKAGE_PIN W3 [get_ports {LED [10]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [10]}] set_property PACKAGE_PIN U3 [get_ports {LED [11]}] Set_prop [L] [get_ports {LED [11]}] set_property PACKAGE_PIN P3 [get_ports {LED [12]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [12]}] set_property PACKAGE_PIN N3 [get_ports {LED [13]}] set_property IOSTANDARD LVC {LED [13]}] set_property PACKAGE_PIN P1 [get_ports {LED [14]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [14]}] set_property PACKAGE_PIN L1 [get_ports {LED [15]}] set_property IOSTANDARD LVCMOS33

set_property PACKAGE_PIN U18 [get_ports BTN] set_property IOSTANDARD LVCMOS33 [get_ports BTN]

set_property PACKAGE_PIN A14 [get_ports {MS [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [0]}] set_property PACKAGE_PIN A16 [get_ports {MS [1]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS] [get_ports {MS] B15 [get_ports {MS [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [2]}] set_property PACKAGE_PIN B16 [get_ports {MS [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [3]}]

Langkah 6: Fail Sumber Utama

Dalam fail utama ini kami menyatukan semua fail sumber komponen yang disebutkan sebelumnya. Fail ini berfungsi sebagai kod struktur yang menyatukan komponen yang berbeza.

entiti Master_Final_Project adalah Port (BTN: dalam STD_LOGIC; CLK: in STD_LOGIC; MS: in STD_LOGIC_VECTOR (3 downto 0); LED: out STD_LOGIC_VECTOR (15 downto 0)); tamat Master_Final_Project;

seni bina Kelakuan Master_Final_Project adalah

komponen final_project adalah Port (--CLK: in STD_LOGIC; NMS: in STD_LOGIC_VECTOR (3 downto 0); BTN: in STD_LOGIC; --sw: in STD_LOGIC_Vector (1 downto 0); LED: out STD_LOGIC_VECTOR (15 downto 0)); komponen akhir;

komponen Final_DFF adalah

Port (CLK: dalam STD_LOGIC; D: dalam STD_LOGIC_Vector (3 ke bawah 0); Q: keluar STD_LOGIC_Vector (3 ke bawah 0)); komponen akhir;

isyarat DFF02proj30: STD_LOGIC;

isyarat DFF12proj74: STD_LOGIC; isyarat DFF22proj118: STD_LOGIC; isyarat DFF32proj1512: STD_LOGIC;

bermula

DFF0: Peta port Final_DFF (CLK => CLK, D (0) => MS (0), D (1) => MS (1), D (2) => MS (2), D (3) => MS (3), Q (0) => DFF02proj30, Q (1) => DFF12proj74, Q (2) => DFF22proj118, Q (3) => DFF32proj1512); Proj0: peta port projek akhir (NMS (0) => DFF02proj30, NMS (1) => DFF12proj74, NMS (2) => DFF22proj118, NMS (3) => DFF32proj1512, BTN => BTN, LED => LED); Tingkah laku akhir;

Langkah 7: Perhimpunan

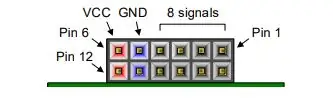

Pemasangan perkakasan untuk projek ini adalah minimum. Kepingan yang diperlukan adalah seperti berikut:

1. Papan basys 3 (1)

2. Sensor gerakan murah yang boleh didapati di amazon di sini. (4)

3. Pemimpin lelaki-ke-wanita (4)

Perhimpunan:

1. Sambungkan 4 petunjuk lelaki ke port JB header JB 1-4 (Lihat Rajah).

2. Sambungkan hujung wanita ke pin output sensor gerakan.

Langkah 8: Memuatkan Program

Sekarang kita bersedia memuatkan fail sumber induk VHDL ke papan Basys 3. Pastikan untuk menjalankan sintesis, pelaksanaan, dan buat pemeriksaan aliran bit untuk sebarang kemungkinan kesilapan. Sekiranya semuanya berjaya dijalankan, buka pengurus perkakasan dan atur cara peranti Basys 3. Projek anda kini selesai!

Disyorkan:

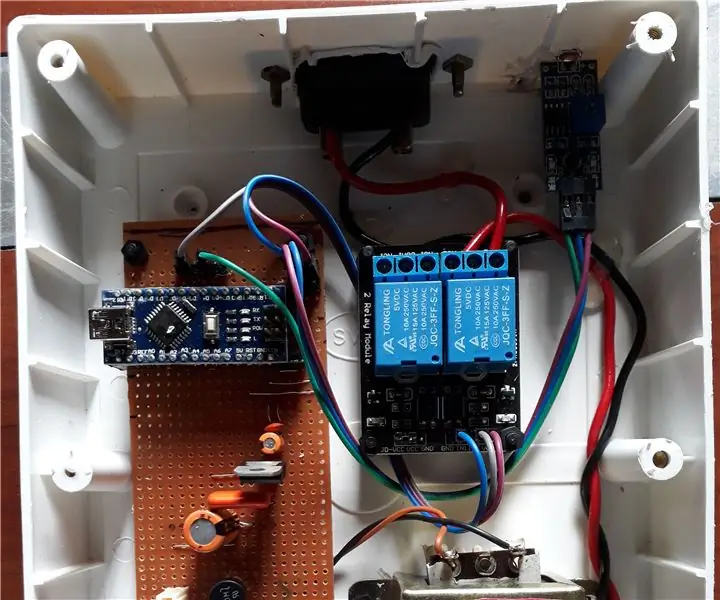

Lampu Jalan Automatik Tenaga Suria DIY: 3 Langkah

Lampu Jalan Automatik DIY Solar Powered: Rumah saya terletak di kawasan luar bandar, jadi jalan di depan rumah saya benar-benar gelap apabila tidak ada cahaya sama sekali. Jadi di sini saya membuat lampu jalan berkuasa solar yang secara automatik menyala ketika matahari terbenam dan mati pada waktu matahari terbit. Ia menggunakan panel solar sebagai

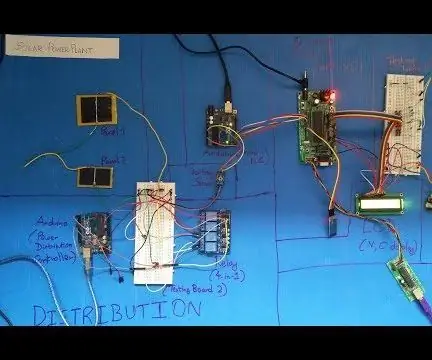

Sistem Pemantauan dan Pengagihan Tenaga Jauh dari Loji Tenaga Suria: 10 Langkah

Sistem Pemantauan dan Pengagihan Tenaga Jauh dari Loji Tenaga Tenaga Suria: Tujuan projek ini adalah untuk memantau dan mengagihkan kuasa dalam sistem kuasa (sistem tenaga suria). Reka bentuk sistem ini dijelaskan secara abstrak seperti berikut. Sistem ini mengandungi pelbagai grid dengan kira-kira 2 panel suria di

Lampu Halaman Interaktif, Lampu Jalan Lorong: 3 Langkah

Lampu Halaman Interaktif, Lampu Jalan Lorong: Saya mahu membina semacam lampu halaman interaktif untuk halaman belakang saya. Idenya adalah, ketika seseorang berjalan sehala ia akan memancarkan animasi ke arah yang anda jalankan. Saya mulakan dengan lampu solar Dollar General $ 1.00

Suis Lampu Diaktifkan Gerakan Dengan Sensor Cahaya: 5 Langkah

Suis Lampu Diaktifkan Gerakan Dengan Sensor Cahaya: Suis lampu diaktifkan gerakan mempunyai banyak aplikasi baik di rumah dan di pejabat. Ini, bagaimanapun, telah menambah kelebihan menggabungkan sensor cahaya, sehingga cahaya ini hanya dapat dipicu pada waktu malam

Radio Tenaga Suria Tenaga Percuma: 4 Langkah (dengan Gambar)

Radio Tenaga Suria Tenaga Percuma: Radio tenaga suria tenaga percuma di https://www.youtube.com/watch?v=XtP7g… adalah projek mudah untuk menukar bateri lama yang dikendalikan radio dalam radio berkuasa solar yang anda boleh panggil tenaga percuma kerana tidak menggunakan bateri dan ia beroperasi ketika matahari