Isi kandungan:

- Pengarang John Day day@howwhatproduce.com.

- Public 2024-01-30 11:10.

- Diubah suai terakhir 2025-01-23 15:01.

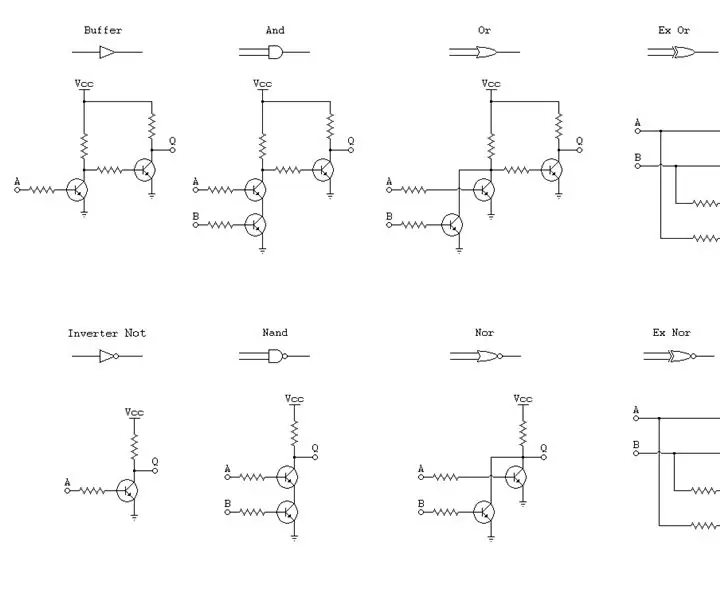

Saya membina gerbang transistor sedikit berbeza daripada kebanyakan jurutera elektronik lain. Kebanyakan orang ketika membina gerbang transistor; membina mereka dengan hanya logik positif dalam fikiran, namun gerbang di IC mempunyai dua logik, logik positif dan logik negatif. Dan saya membina gerbang transistor saya dengan logik positif dan negatif.

Walaupun ada lapan pintu; Penyangga, Inverter atau Tidak, Dan, Nand, Or, Nor, Xor, dan Xnor, ia dibuat dari tiga litar pintu. Dan ketika anda membina gerbang logik dua, tiga litar yang digunakan untuk membina gerbang adalah Inverter atau Not, Nand, dan Nor, selebihnya gerbang dibuat dari dua atau lebih dari ketiga-tiga gerbang ini.

Mengapa membina gerbang transistor? Inilah lima sebab untuk membina pintu pagar anda sendiri.

1. Anda tidak mempunyai pintu pagar yang anda perlukan.

2. Anda mahukan gerbang yang membawa lebih banyak kuasa daripada IC gerbang standard.

3. Anda hanya mahukan satu pintu dan anda benci membuang sisa gerbang di IC.

4. Kos, satu transistor Inverter kurang dari $ 0.25 dan hex Inverter IC adalah $ 1.00 ke atas.

5. Anda mahu memahami gerbang dengan lebih baik.

Langkah 1: Alat & Bahagian

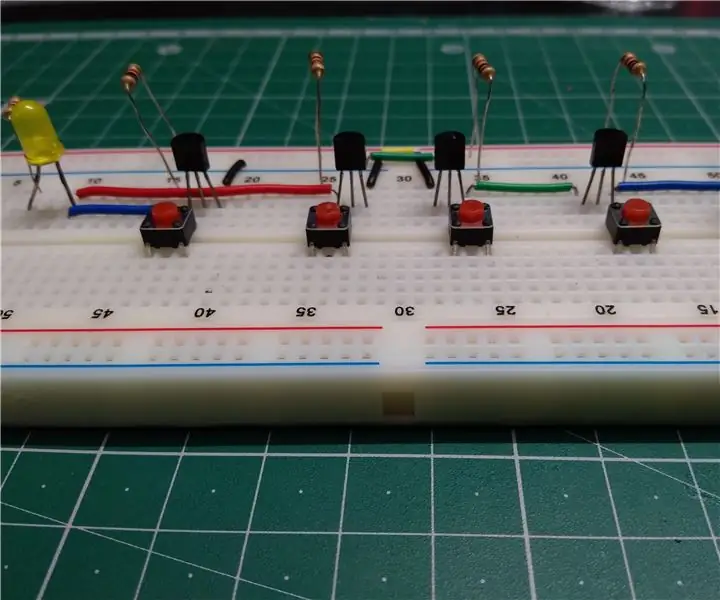

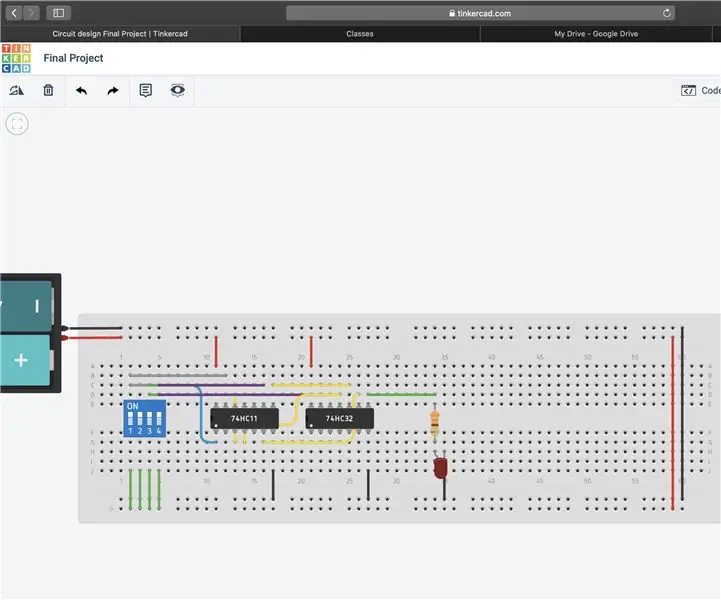

Gerbang dalam Instructable ini adalah gerbang ¼ watt jika anda ingin membina gerbang dengan watt yang lebih tinggi, anda memerlukan komponen watt yang lebih tinggi.

Wayar Pelompat

Papan roti

Bekalan Kuasa

1 x SN74LS04 IC

2 x Suis

2 x LED 1 merah 1 hijau

Perintang 2 x 820 Ω ¼ w

Perintang 2 x 1 kΩ ¼ w

Perintang 3 x 10 kΩ ¼ w

3 x transistor tujuan umum NPN, saya menggunakan 2N3904.

2 x transistor tujuan am PNP, saya menggunakan 2N3906.

Langkah 2: Logik Dwi

Apabila anda melihat jadual kebenaran gerbang; seperti dua input Atau gerbang, anda akan mendapat jadual kebenaran yang kelihatan seperti ini. Ini adalah jadual kebenaran positif untuk gerbang Or. Di bawah A dan B adalah input ke pintu dan Q adalah output. 1 mewakili nilai logik 1 atau + 5 volt dan 0 mewakili nilai logik 0 atau 0 volt. Oleh itu, apabila kebanyakan orang membina pintu keluar dari transistor, mereka membina nilai logik 1 atau + 5 volt dan nilai logik 0 atau tidak volt. Tetapi bukan itu yang berlaku pada output gerbang, dalam IC.

Apabila output gerbang beralih dari nilai logik 1 ke nilai logik 0 output gerbang itu berubah dari + 5 volt dengan arus mengalir keluar dari output ke 0 volt dengan arus mengalir ke output pintu. Arus membalikkan arah. Apabila anda menggunakan aliran arus terbalik ini disebut logik negatif di mana 0 volt adalah - 1 nilai logik dan + 5 volt adalah - 0 nilai logik.

Paling mudah untuk melihat apa yang dilakukannya ialah apabila anda menyambungkan output dari mana-mana gerbang; ke pangkal transistor NPN dan transistor PNP, bersiri dengan LED. Walaupun keluaran gerbang adalah nilai logik 1, (5 Volt), transistor NPN ditutup dan LED secara bersiri dengan transistor NPN menyala. Apabila output gerbang beralih dari nilai logik 1 ke nilai logik 0, (5 volt hingga 0 volt), arus membalikkan arah dan transistor NPN terbuka ketika transistor PNP ditutup. Ini mematikan LED secara bersiri dengan transistor NPN dan menyalakan LED secara bersiri dengan transistor PNP.

Gerbang transistor saya mempunyai logik dwi yang sama dengan gerbang di IC. Walaupun keluaran gerbang adalah nilai logik 1, (5 Volt), transistor NPN ditutup dan LED secara bersiri dengan transistor NPN menyala. Apabila output gerbang beralih dari nilai logik 1 ke nilai logik 0, (5 volt hingga 0 volt), arus membalikkan arah dan transistor NPN terbuka ketika transistor PNP ditutup. Ini mematikan LED secara bersiri dengan transistor NPN dan menyalakan LED secara bersiri dengan transistor PNP.

Langkah 3: Tidak atau Inverter Gate

Not atau Inverter gate adalah yang pertama dari 3 pintu yang diperlukan untuk membuat 5 pintu yang lain.

Apabila input, (A) gerbang Inverter 0 atau 0 volt transistor NPN terbuka dan outputnya, (Q) adalah 1 atau +5 volt dan sebarang arus positif keluar dari output (Q).

Apabila input, (A) pintu Inverter adalah 1 atau +5 volt transistor NPN ditutup dan outputnya, (Q) adalah 0 atau 0 volt dan sebarang arus positif masuk ke tanah melalui transistor.

Langkah 4: Nand Gate

Gerbang Nand adalah pintu kedua dari tiga pintu yang diperlukan untuk membuat 5 pintu yang lain.

Apabila input, (A dan B) dari gerbang Nand adalah 0 atau 0 volt kedua-dua transistor NPN terbuka dan outputnya, (Q) adalah 1 atau +5 volt dan sebarang arus positif keluar dari output (Q).

Apabila input, (A) gerbang Nand adalah 1 atau +5 volt transistor NPN pada input A ditutup. Dan apabila input, (B) gerbang Nand adalah 0 atau 0 volt transistor NPN pada input B terbuka dan outputnya, (Q) adalah 1 atau +5 volt dan sebarang arus positif keluar dari output (Q).

Apabila input, (A) gerbang Nand adalah 0 atau 0 volt transistor NPN pada input A terbuka. Dan apabila input, (B) gerbang Nand adalah 1 atau +5 volt transistor NPN pada input B ditutup dan outputnya, (Q) adalah 1 atau +5 volt dan sebarang arus positif keluar dari output (Q).

Apabila input, (A dan B) dari gerbang Nand adalah 1 atau +5 volt kedua-dua transistor NPN ditutup dan outputnya, (Q) adalah 0 atau 0 volt dan sebarang arus positif masuk ke tanah melalui transistor.

Langkah 5: Pintu Nor

Pintu Nor adalah yang ketiga dari tiga pintu yang diperlukan untuk membuat 5 pintu yang lain.

Apabila input, (A dan B) dari gerbang Nor adalah 0 atau 0 volt kedua-dua transistor NPN terbuka dan outputnya, (Q) adalah 1 atau +5 volt dan sebarang arus positif keluar dari output (Q).

Apabila input, (A) pintu Nor adalah 1 atau +5 volt transistor NPN pada input A ditutup. Dan apabila input, (B) dari gerbang Nor adalah 0 atau 0 volt transistor NPN pada input B terbuka dan outputnya, (Q) adalah 0 atau 0 volt dan sebarang arus positif masuk ke tanah melalui transistor pada input A.

Apabila input, (A) pintu Nor adalah 0 atau 0 volt transistor NPN pada input A terbuka. Dan apabila input, (B) gerbang Nor adalah 1 atau +5 volt transistor NPN pada input B ditutup dan outputnya, (Q) adalah 0 atau 0 volt dan sebarang arus positif masuk ke tanah melalui transistor pada B input.

Apabila input, (A dan B) gerbang Nor adalah 1 atau +5 volt kedua-dua transistor NPN ditutup dan outputnya, (Q) adalah 0 atau 0 volt dan sebarang arus positif masuk ke tanah melalui kedua-dua transistor.

Langkah 6: Penyangga

Penyangga menggunakan dua pintu pagar yang sama; dua gerbang Not atau Inverter secara bersiri.

Apabila input, (A) pintu Inverter pertama adalah 0 atau 0 volt transistor NPN terbuka dan outputnya, adalah 1 atau +5 volt ke input penyongsang kedua. Apabila input gerbang Inverter kedua adalah 1 atau +5 volt transistor NPN ditutup dan outputnya, (Q) adalah 0 atau 0 volt dan sebarang arus positif masuk ke tanah melalui transistor.

Apabila input, (A) pintu Inverter pertama adalah 1 atau +5 volt transistor NPN ditutup dan outputnya, adalah 0 atau 0 volt ke input penyongsang kedua. Apabila input gerbang Inverter kedua 0 atau 0 volt transistor NPN terbuka dan outputnya, (Q) adalah 1 atau +5 volt dan sebarang arus positif keluar output (Q).

Langkah 7: Dan Pintu

Gerbang And adalah gerbang Nand dan gerbang Not atau Inverter secara bersiri.

Inputnya sama dengan gerbang Nand namun outputnya dibalikkan oleh gerbang Not atau Inverter.

Apabila input, (A dan B) gerbang And adalah 0 atau 0 volt kedua-dua transistor NPN terbuka, output gerbang pertama adalah 1 atau +5 volt. Apabila input pintu Inverter adalah 1 atau +5 volt transistor NPN ditutup dan outputnya, (Q) adalah 0 atau 0 volt dan sebarang arus positif masuk ke tanah melalui transistor.

Apabila input, (A) gerbang And adalah 1 atau +5 volt transistor NPN pada input A ditutup. Dan apabila input, (B) gerbang And 0 atau 0 volt transistor NPN pada input B terbuka, output gerbang pertama adalah 1 atau +5 volt. Apabila input pintu Inverter adalah 1 atau +5 volt transistor NPN ditutup dan outputnya, (Q) adalah 0 atau 0 volt dan sebarang arus positif masuk ke tanah melalui transistor.

Apabila input, (A) gerbang And adalah 0 atau 0 volt transistor NPN pada input A terbuka. Dan apabila input, (B) gerbang And adalah 1 atau +5 volt transistor NPN pada input B ditutup, output gerbang pertama adalah 1 atau +5 volt. Apabila input pintu Inverter adalah 1 atau +5 volt transistor NPN ditutup dan outputnya, (Q) adalah 0 atau 0 volt dan sebarang arus positif masuk ke tanah melalui transistor.

Apabila input, (A dan B) gerbang Nand adalah 1 atau +5 volt kedua-dua transistor NPN ditutup dan output gerbang pertama adalah 0 atau 0 volt. Apabila input gerbang Inverter 0 atau 0 volt transistor NPN terbuka dan outputnya, (Q) adalah 1 atau +5 volt dan sebarang arus positif keluar output (Q).

Langkah 8: Atau Pintu

Gerbang Or adalah gerbang Nor dan gerbang Not atau Inverter secara bersiri.

Inputnya sama dengan gerbang Nor namun output dibalikkan oleh gerbang Not atau Inverter.

Apabila input, (A dan B) gerbang Or adalah 0 atau 0 volt kedua-dua transistor NPN terbuka, output gerbang pertama adalah 1 atau +5 volt. Apabila input pintu Inverter adalah 1 atau +5 volt transistor NPN ditutup dan outputnya, (Q) adalah 0 atau 0 volt dan sebarang arus positif masuk ke tanah melalui transistor.

Apabila input, (A) gerbang Or adalah 1 atau +5 volt transistor NPN pada input A ditutup. Dan apabila input, (B) dari pintu Nor adalah 0 atau 0 volt transistor NPN pada input B terbuka dan output dari gerbang pertama adalah 0 atau 0 volt. Apabila input gerbang Inverter 0 atau 0 volt transistor NPN terbuka dan outputnya, (Q) adalah 1 atau +5 volt dan sebarang arus positif keluar output (Q).

Apabila input, (A) gerbang Or adalah 0 atau 0 volt transistor NPN pada input A terbuka. Dan apabila input, (B) pintu Nor adalah 1 atau +5 volt transistor NPN pada input B ditutup dan output pintu pertama adalah 0 atau 0 volt. Apabila input pintu Inverter 0 atau 0 volt transistor NPN terbuka dan outputnya, (Q) adalah 1 atau +5 volt dan sebarang arus positif keluar output (Q).

Apabila input, (A dan B) gerbang Or adalah 1 atau +5 volt kedua-dua transistor NPN ditutup dan output gerbang pertama adalah 0 atau 0 volt. Apabila input gerbang Inverter 0 atau 0 volt transistor NPN terbuka dan outputnya, (Q) adalah 1 atau +5 volt dan sebarang arus positif keluar output (Q).

Langkah 9: Nor Gate Eksklusif (Xnor)

Pintu eksklusif Nor dikonfigurasikan sebagai dua gerbang Nand yang dihubungkan secara selari sebagai gerbang Nor dengan dua transistor PNP transistor teratas.

Apabila input, (A dan B) gerbang Xnor adalah 0 atau 0 volt kedua-dua transistor NPN terbuka dan kedua-dua transistor PNP ditutup. Output, (Q) adalah 1 atau +5 volt dan sebarang arus positif keluar dari output (Q).

Apabila input, (A) gerbang Xnor adalah 1 atau +5 volt transistor NPN pada input A ditutup dan transistor PNP terbuka. Dengan input, (B) gerbang Xnor adalah 0 atau 0 volt transistor PNP pada input B ditutup dan transistor NPN terbuka. Keluarannya, (Q) ialah 0 atau 0 volt dan arus positif mana-mana ke tanah melalui transistor tertutup.

Apabila input, (A) gerbang Xnor adalah 0 atau 0 volt transistor NPN pada input A terbuka dan transistor PNP ditutup. Dengan input, (B) gerbang Xnor adalah 1 atau +5 volt transistor PNP pada input B terbuka dan transistor NPN ditutup. Output, (Q) adalah 0 atau 0 volt dan sebarang arus positif masuk ke tanah melalui transistor tertutup.

Apabila input, (A dan B) gerbang Xnor adalah 1 atau +5 volt kedua-dua transistor NPN ditutup dan kedua-dua transistor PNP terbuka. Output, (Q) adalah 1 atau +5 volt dan sebarang arus positif keluar dari output (Q).

Langkah 10: Eksklusif atau Gerbang (Xor)

Pintu Eksklusif Atau; menggunakan ketiga-tiga gerbang kunci, ia dikonfigurasikan sebagai dua gerbang Nand yang disambungkan secara selari sebagai gerbang Nor dengan dua transistor PNP transistor atas dan gerbang Not atau Inverter secara bersiri.

Input gerbang Xor sama dengan gerbang Xnor namun output dibalikkan oleh gerbang Not atau Inverter.

Apabila input, (A dan B) gerbang Xnor adalah 0 atau 0 volt kedua-dua transistor NPN terbuka dan kedua-dua transistor PNP ditutup dan output set gerbang pertama adalah 1 atau +5 volt. Apabila input pintu Inverter adalah 1 atau +5 volt transistor NPN ditutup dan outputnya, (Q) adalah 0 atau 0 volt dan sebarang arus positif masuk ke tanah melalui transistor.

Apabila input, (A) gerbang Xnor adalah 1 atau +5 volt transistor NPN pada input A ditutup dan transistor PNP terbuka. Dengan input, (B) gerbang Xnor adalah 0 atau 0 volt transistor PNP pada input B ditutup dan transistor NPN terbuka, 0 atau 0 volt ke input Inverter. Apabila input pintu Inverter 0 atau 0 volt transistor NPN terbuka dan outputnya, (Q) adalah 1 atau +5 volt dan sebarang arus positif keluar output (Q).

Apabila input, (A) gerbang Xnor adalah 0 atau 0 volt transistor NPN pada input A terbuka dan transistor PNP ditutup. Dengan input, (B) pintu Xnor adalah 1 atau +5 volt transistor PNP pada input B terbuka dan transistor NPN ditutup, 0 atau 0 volt ke input Inverter. Apabila input pintu Inverter 0 atau 0 volt transistor NPN terbuka dan outputnya, (Q) adalah 1 atau +5 volt dan sebarang arus positif keluar output (Q).

Apabila input, (A dan B) gerbang Xnor adalah 1 atau +5 volt kedua-dua transistor NPN ditutup dan kedua-dua transistor PNP terbuka Apabila input gerbang Inverter kedua adalah 1 atau +5 volt NPN transistor ditutup dan output, (Q) adalah 0 atau 0 volt dan sebarang arus positif menuju ke tanah melalui transistor.

Naib Johan dalam Cabaran Petua & Trik Elektronik

Disyorkan:

Gerbang Logik Menggunakan Transistor: 3 Langkah

Logic Gates Menggunakan Transistor: Gerbang logik adalah blok asas bagi mana-mana sistem digital

Buat Penganalisis Logik Digital dengan Langkah Kurang Dari $ 1: 5

Buat Penganalisis Logik Digital dengan Kurang Dari $ 1: Sensor tahap logik adalah peranti yang merasakan jika output komponen adalah 1 atau 0 (positif atau negatif). Anda tahu sensor tahap yang bagus dengan skrin LCD yang harganya sekitar $ 25? Yang ini lebih murah dan melakukan perkara yang sama (I

Jumlah Litar Produk Menggunakan Gerbang Logik: 4 Langkah

Jumlah Litar Produk Menggunakan Gerbang Logik: Dalam petunjuk ini, saya akan menunjukkan kepada anda bagaimana membuat sistem anda sendiri menggunakan jumlah produk, sedikit aljabar Boolean, dan beberapa gerbang logik. Anda tidak perlu membuat sistem tepat yang sama dengan yang terdapat dalam tutorial ini, tetapi anda boleh menggunakan

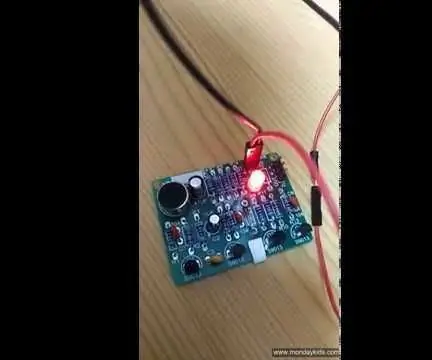

Cara Membuat Transistor Ganda D882 ke Penguat Audio: 9 Langkah

Cara Membuat D882 Double Transistor ke Audio Amplifier: Hai kawan, Hari ini saya akan membuat litar Penguat Audio menggunakan transistor D882 Double. Mari kita mulakan

Litar Logik Kawalan Bunyi Lucu DIY Dengan Hanya Transistor Kapasitor Transistor: 6 Langkah

Litar Logik Kawalan Bunyi Lucu DIY Dengan Hanya Transistor Kapasitor Transistor: Pada masa ini terdapat trend menaik dalam merancang litar dengan IC (Integrated Circuit), banyak fungsi yang perlu disedari oleh litar analog pada masa lalu tetapi sekarang juga dapat dipenuhi oleh IC bahawa ia lebih stabil dan senang dan senang