Isi kandungan:

- Pengarang John Day [email protected].

- Public 2024-01-30 11:07.

- Diubah suai terakhir 2025-01-23 15:00.

Dalam tutorial ini, kita akan menulis kod Verilog untuk mengawal motor servo. Servo SG-90 dihasilkan oleh Waveshare. Semasa anda membeli motor servo, anda mungkin akan menerima lembaran data yang menyenaraikan voltan operasi, tork maksimum dan Modul Lebar Lebar (PWM) yang dicadangkan … dll. Walau bagaimanapun, FPGA DuePrologic memberikan voltan input 3.3V di mana voltan operasi servo SG-90 adalah 5V - 7V. Dengan kekurangan kuasa elektrik, saya akan menyenaraikan PWM saya yang dikalibrasi untuk berjaya memutar motor servo.

Tugas kami: Motor servo diputar berulang-alik dengan jangka masa 5 saat

Menu penuh:

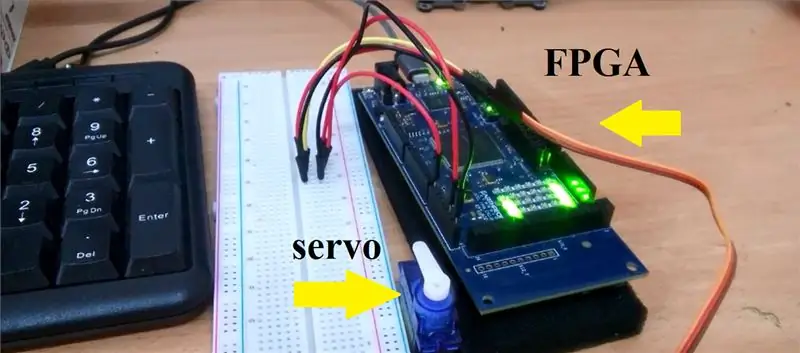

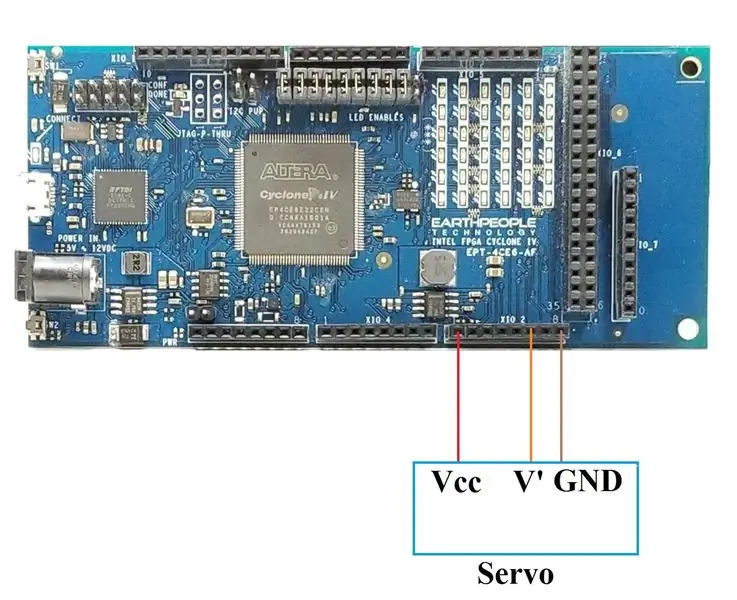

Langkah 1: Bina Litar Elektronik

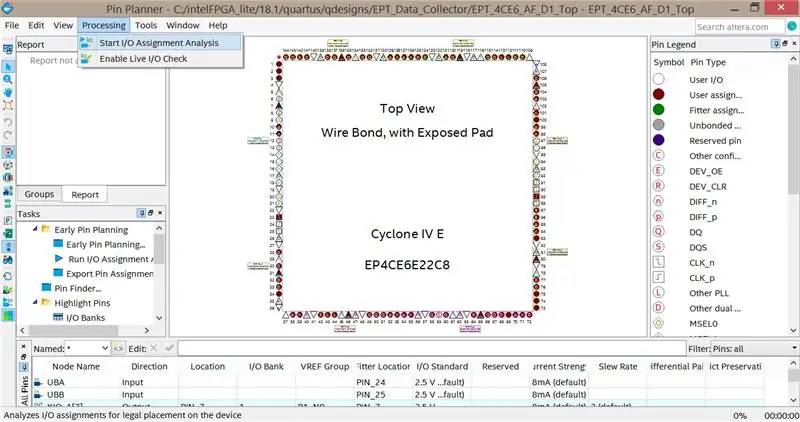

Langkah 2: Sediakan Pin Perancang

Klik "Mulakan Analisis Tugasan I / O" untuk memeriksa sama ada perancang pin diset dengan betul. Jika tidak, anda mesti mengimport semua nama port sendiri.

Langkah 3: Kod Verilog

Kami membuat pemasa "servo_count". Apabila "servo_A" TINGGI, PWM adalah 1.5ms dan oleh itu servo terletak pada 120 deg. Sebaliknya, apabila "servo_A" RENDAH, PWM adalah 0.15ms dan oleh itu servo kekal pada 0 darjah.

tetapkan XIO_2 [3] = servo_pulse; // untuk V '

reg [31: 0] servo_count;

permulaan awal

servo_count <= 32'b0;

servo_A <= 1'b0;

akhir

selalu @ (posedge CLK_66)

bermula

servo_count <= servo_count + 1'b1;

jika (servo_count> 400000000) // Kitaran jam 66MHz, 1 / 66M * 400000000 ~ 5 saat

bermula

servo_A <=! servo_A;

servo_count <= 32'b0;

akhir

akhir

reg [31: 0] ex_auto;

permulaan awal

ex_auto <= 32'b0;

servo_auto <= 1'b0;

akhir

selalu @ (posedge CLK_66)

bermula

jika (servo_A == 1'b1)

bermula

ex_auto <= ex_auto + 1'b1;

jika (ex_auto> 100000) // Kitaran jam 66MHz, PWM ini ialah ~ 1.5ms, servo berputar hingga 120 deg

bermula

servo_auto <=! servo_auto;

ex_auto <= 32'b0;

akhir

akhir

jika (servo_A == 1'b0)

bermula

ex_auto <= ex_auto + 1'b1;

jika (ex_auto> 10000) // Kitaran jam 66MHz, PWM ini adalah ~ 0.15ms, servo berputar hingga 0 deg

bermula

servo_auto <=! servo_auto;

ex_auto <= 32'b0;

akhir

akhir

akhir

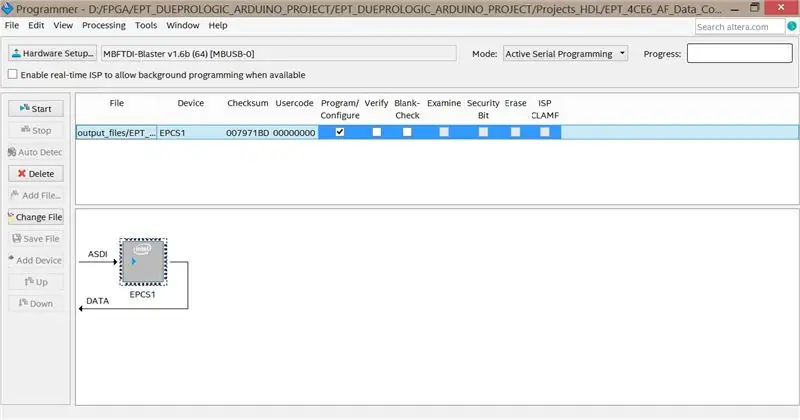

Langkah 4: Muat naik Kod Verilog

Klik "Mulakan Penyusunan". Sekiranya tidak ada mesej ralat yang ditampilkan, pergi ke "Programmer" untuk menyelesaikan persediaan perkakasan. Ingatlah untuk mengemas kini fail pof dalam "Ubah fail" jika perlu. Klik "Mula" untuk memuat naik kod.

Bagaimanapun, anda mesti melihat bahawa motor servo diputar secara berkala.

Disyorkan:

FPGA Cyclone IV DueProLogic Controls Raspberry Pi Kamera: 5 Langkah

FPGA Cyclone IV DueProLogic Controls Raspberry Pi Camera: Walaupun FPGA DueProLogic secara rasmi direka untuk Arduino, kami akan menjadikan FPGA dan Raspberry Pi 4B dapat disambungkan. Tiga tugas dilaksanakan dalam tutorial ini: (A) Serentak tekan dua butang tekan pada FPGA untuk membalik sudut

FPGA Cyclone IV DueProLogic - Butang Tekan & LED: 5 Langkah

FPGA Cyclone IV DueProLogic - Butang Tekan & LED: Dalam tutorial ini, kita akan menggunakan FPGA untuk mengawal litar LED luaran. Kami akan melaksanakan tugas berikut (A) Gunakan butang tekan pada FPGA Cyclone IV DuePrologic untuk mengawal LED. (B) Lampu LED menyala & dimatikan secara berkala Makmal demo Video

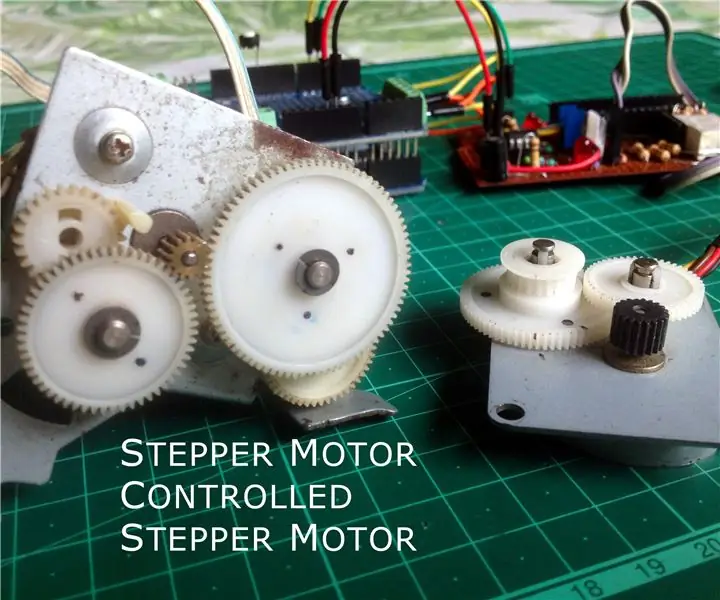

Stepper Motor terkawal Motor Stepper - Motor Stepper Sebagai Pengekod Rotary: 11 Langkah (dengan Gambar)

Stepper Motor terkawal Motor Stepper | Stepper Motor Sebagai Rotary Encoder: Adakah beberapa motor stepper berbaring dan mahu melakukan sesuatu? Dalam Instructable ini, mari gunakan motor stepper sebagai rotary encoder untuk mengawal kedudukan motor stepper lain menggunakan mikrokontroler Arduino. Jadi tanpa basa-basi lagi, mari kita

Lengan Robot Motor Servo RC Terkawal Fpga - Peraduan Digilent: 3 Langkah

Lengan Robot Motor Servo RC Terkawal Fpga - Peraduan Digilent: Lengan robot motor servo terkawal FPGA Matlamat projek ini adalah untuk mewujudkan sistem yang dapat diprogramkan yang dapat melakukan operasi pematerian pada papan perf. Sistem ini didasarkan pada papan pengembangan Digilent Basys3 dan ia akan dapat

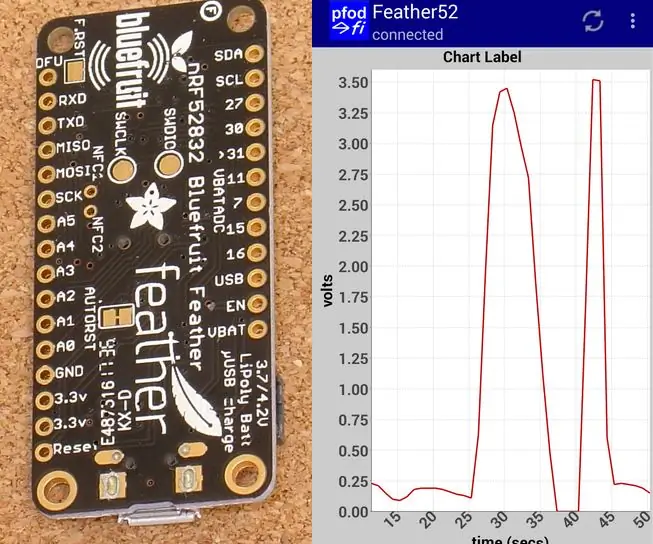

Adafruit Feather NRF52 Custom Controls, Tidak Perlu Pengekodan: 8 Langkah (dengan Gambar)

Adafruit Feather NRF52 Kawalan Tersuai, Tidak Perlu Pengekodan: Kemas kini 23 April 2019 - Untuk plot tarikh / masa yang hanya menggunakan Arduino millis () lihat Arduino Tarikh / Masa Memplot / Log menggunakan Millis () dan PfodApp PfodDesigner V3.0.3610 + terbaru percuma yang dihasilkan lengkapkan lakaran Arduino untuk memplot data berdasarkan tarikh / masa anda