Isi kandungan:

- Pengarang John Day day@howwhatproduce.com.

- Public 2024-01-30 11:10.

- Diubah suai terakhir 2025-01-23 15:01.

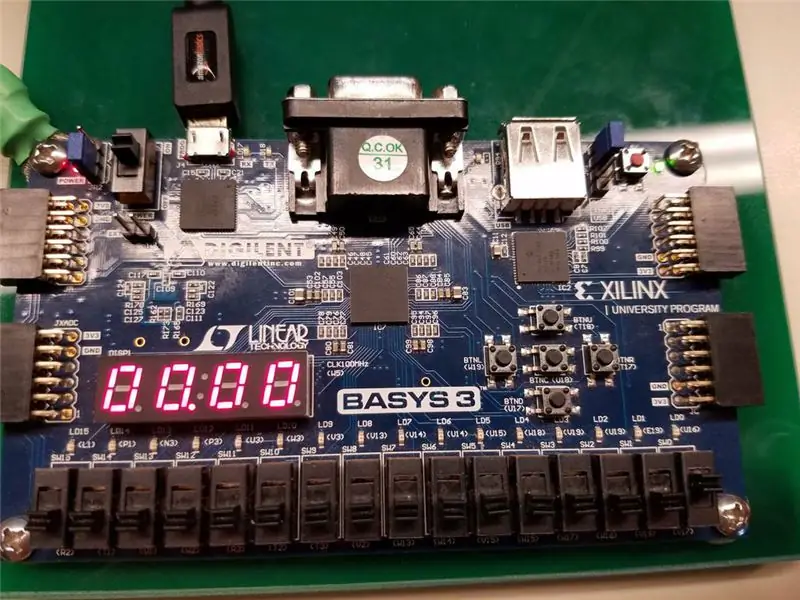

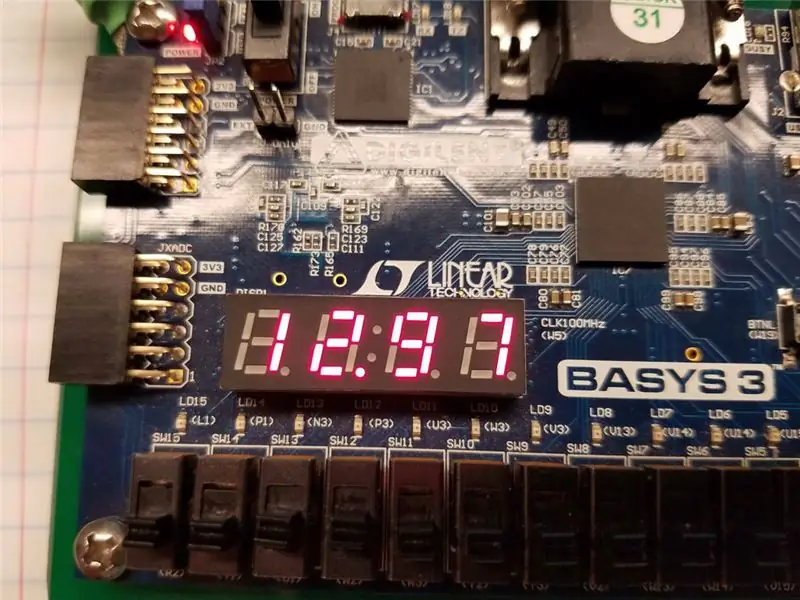

Selamat datang di instruksional mengenai cara membina jam randik menggunakan papan asas VHDL dan Basys 3. Kami teruja untuk berkongsi projek kami dengan anda! Ini adalah projek akhir untuk kursus CPE 133 (Reka Bentuk Digital) di Cal Poly, SLO pada Musim Gugur 2016. Projek yang kami bina adalah jam randik ringkas yang bermula, diset semula, dan berhenti sebentar. Ia memerlukan tiga butang tekan pada papan Basys3 sebagai input, dan waktunya dipaparkan pada paparan tujuh segmen empat digit papan. Masa yang berlalu dipaparkan dalam beberapa saat: format sentimeter. Ia menggunakan jam sistem papan sebagai input untuk melacak waktu yang berlalu dan mengeluarkan waktu ke empat digit paparan tujuh segmen.

Langkah 1: Bahan

Bahan yang anda perlukan untuk projek ini:

- 1 komputer dengan Vivado Design Suite WebPack dipasang dari Xilinx (lebih suka versi 2016.2)

- 1 papan Digilent Basys3 Xilinx Artix-7 FPGA

- 1 kabel port USB

Langkah 2: Menetapkan Input dan Output

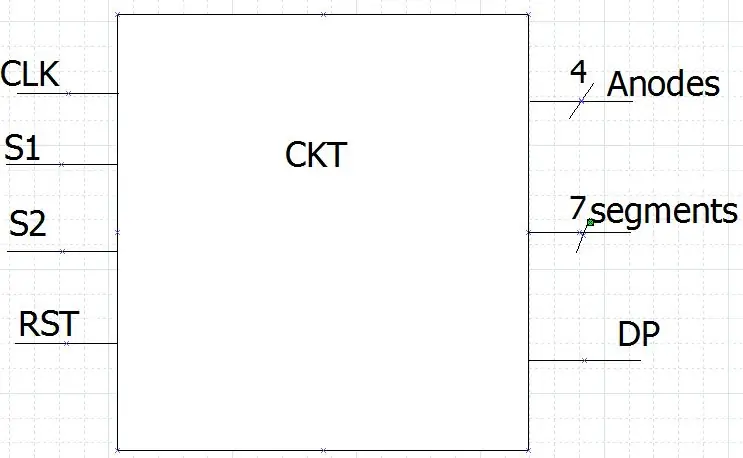

Gambar di atas menunjukkan gambarajah blok tingkat atas modul jam randik utama. Jam randik mengambil input "CLK" (jam), "S1" (butang mula), "S2" (butang jeda), dan "RST" (reset) dan mempunyai output 4-bit "Anod", 7-bit keluaran "segmen", dan output bit tunggal "DP" (titik perpuluhan). Apabila input "S1" tinggi, jam randik mula mengira masa. Apabila "S2" rendah, jam randik berhenti masa. Apabila "RST" tinggi, jam randik berhenti dan mengatur semula masa. Terdapat empat submodul dalam litar: pembahagi jam, pembilang digit, pemacu paparan tujuh segmen, dan pengekod paparan tujuh segmen. Modul utama jam randik menghubungkan semua submodul bersama dan ke input dan output.

Langkah 3: Membuat Jam

Modul pembahagi jam mengambil jam sistem dan menggunakan input pembahagi untuk membuat jam dengan kelajuan tidak lebih besar daripada jam sistem. Jam randik menggunakan dua modul jam yang berbeza, satu menghasilkan jam 500 Hz dan jam yang lain menghasilkan jam 100 Hz. Skema untuk pembahagi jam ditunjukkan dalam gambar di atas. Pembahagi jam mengambil input bit tunggal "CLK", dan input 32-bit "Divisor" dan output bit tunggal "CLKOUT". "CLK" adalah jam sistem dan "CLKOUT" adalah jam yang dihasilkan. Modul ini juga merangkumi gerbang NOT, yang menukar isyarat "CLKTOG" apabila kiraan mencapai nilai pembahagi.

Langkah 4: Membilang hingga Sepuluh

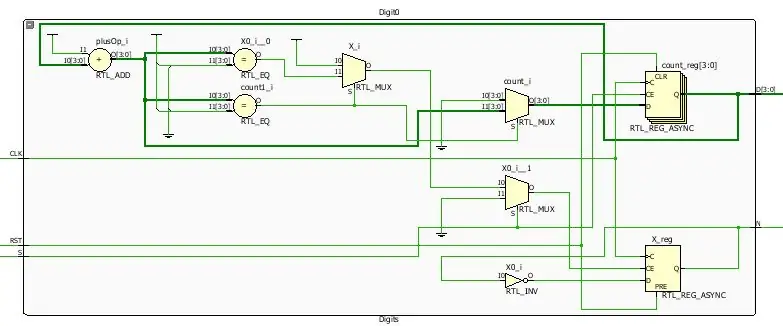

Pembilang digit mengira setiap digit dari 0 hingga 10 dan membuat jam yang lain untuk digit seterusnya berfungsi daripada osilasi itu apabila kiraan mencapai 10. Modul mengambil 3 input bit tunggal "S", "RST", dan "CLK "dan menghasilkan output satu bit" N "dan output 4-bit" D ". Input "S" adalah pengaktifan input. Jam menyala ketika "S" tinggi dan mati ketika "S" rendah. "RST" adalah input semula sehingga jam diset semula apabila "RST" tinggi. "CLK" adalah input jam untuk pembilang digit. "N" adalah output jam yang menjadi jam input untuk digit seterusnya. Output "D" menunjukkan nilai binari digit di mana kaunter berada.

Langkah 5: Memaparkan Nombor

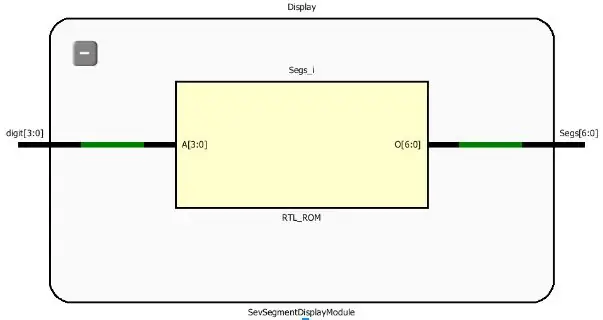

Pengekod paparan tujuh segmen akan menyandikan nombor perduaan yang diterima dari modul pemacu paparan tujuh segmen dan mengubahnya menjadi aliran bit yang akan ditafsirkan sebagai nilai '1' atau '0' untuk setiap segmen paparan. Nombor perduaan diterima oleh modul sebagai "digit" input 4-bit dan menghasilkan "segmen" keluaran 7-bit. Modul ini terdiri daripada blok proses kes tunggal yang memberikan aliran 7-bit khusus untuk setiap kemungkinan nilai input dari 0 hingga 9. Setiap bit dalam aliran tujuh-bit mewakili salah satu daripada tujuh segmen digit pada paparan. Urutan segmen dalam aliran adalah "abcdefg" dengan '0 mewakili segmen yang menyala untuk nombor yang diberikan.

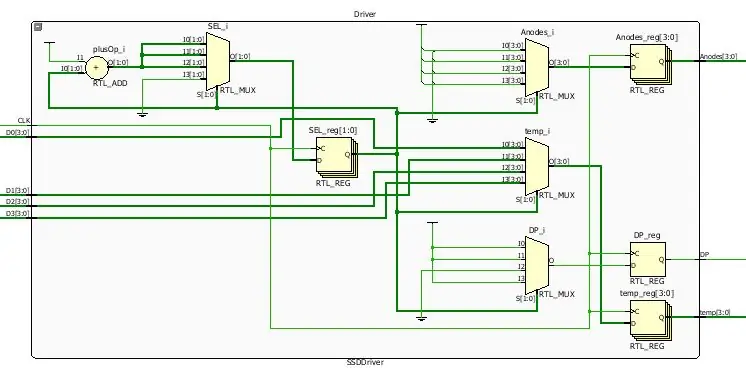

Langkah 6: Cara Memaparkan Jam Randik

Dalam modul pemacu paparan tujuh segmen, terdapat empat input 4-bit "D0", "D1", "D2", dan "D3", masing-masing mewakili empat digit yang akan dipaparkan. Input "CLK" adalah input jam sistem. Output bit tunggal "DP" mewakili titik perpuluhan pada paparan tujuh segmen. Output 4-bit "Anodes" menentukan digit mana pada paparan tujuh segmen yang ditunjukkan dan output "temp" 4-bit bergantung pada keadaan input kawalan 2-bit "SEL". Modul ini menggunakan 4 multiplexer untuk input kawalan "SEL" dan tiga output; "Anod", "temp", dan "DP".

Langkah 7: Bawa Bersama

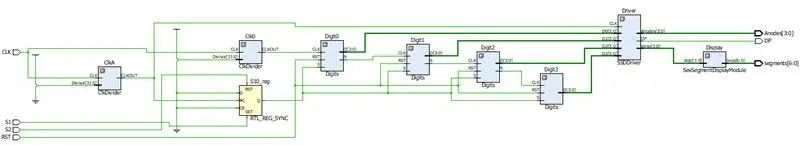

Blok proses 'if' yang berjalan pada jam 500Hz digunakan untuk membuat butang mula dan jeda. Kemudian hubungkan semua submodul bersama dalam modul utama jam randik dengan menyatakan komponen setiap submodul individu dan menggunakan pelbagai isyarat. Subodul digit mengambil output jam dari submodul digit sebelumnya dengan yang pertama mengambil jam 100Hz. Output "D" dari submodul digit kemudian menjadi input "D" dari modul pemacu paparan tujuh segmen. Dan terakhir output "temp" dari modul pemacu paparan tujuh segmen menjadi input "temp" dari modul pengekod tujuh segmen.

Langkah 8: Kekangan

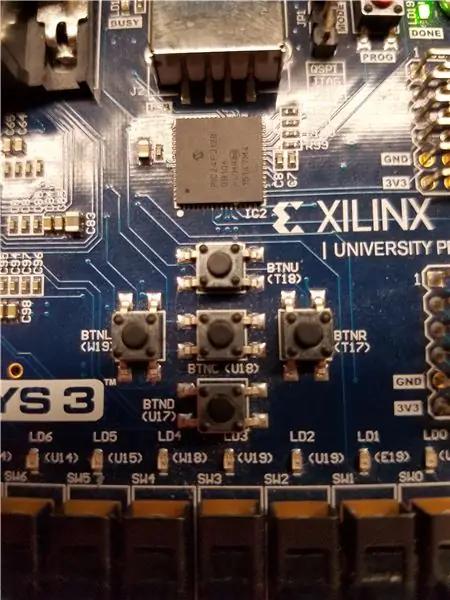

Gunakan 3 butang tekan (W19, T17, dan U18) untuk input "RST", "S1", dan "S2". W19 adalah butang reset, T17 adalah butang mula (S1), dan U18 adalah butang jeda (S2). Kekangan untuk input input jam juga diperlukan menggunakan port W5. Juga, ingat untuk menambahkan baris ini pada kekangan jam:

create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports {CLK}]

Pautkan juga Anoda dan segmen ke papan sehingga jam randik dipaparkan pada paparan tujuh segmen seperti yang dilihat dalam fail kekangan.

Langkah 9: Menguji

Pastikan peranti anda berfungsi dengan bermain dengan tiga butang: menekan dan menahannya dalam setiap urutan yang mungkin untuk mencari kemungkinan masalah dengan kod anda.

Disyorkan:

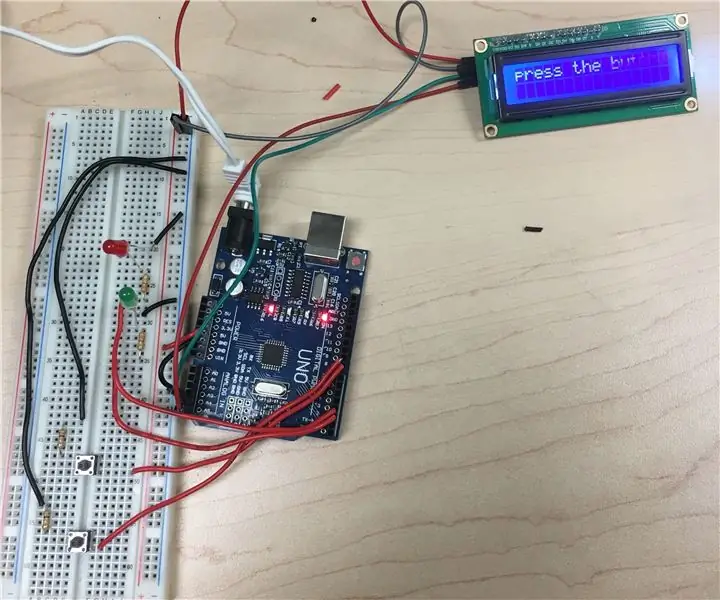

Jam Randik Arduino Menggunakan LCD I2C: 5 Langkah

Arduino Stopwatch Menggunakan I2C LCD: Dalam projek ini saya akan mengajar anda untuk menggunakan paparan LCD dan Arduino sebagai jam randik interaktif. Apabila projek anda selesai dengan kod yang disediakan, ia akan kelihatan seperti foto di atas. Pergi ke langkah seterusnya untuk mengetahui di mana hendak bermula

Cara Membuat Jam Randik Menggunakan Arduino: 8 Langkah (dengan Gambar)

Cara Membuat Jam Randik Menggunakan Arduino: Ini Jam Ringkas Paparan Arduino 16 * 2 Lcd Yang Sangat Sederhana ……….. Sekiranya Anda Suka Ini Boleh Diperintahkan Sila Langgan Saluran Saya https://www.youtube.com / ZenoModiff

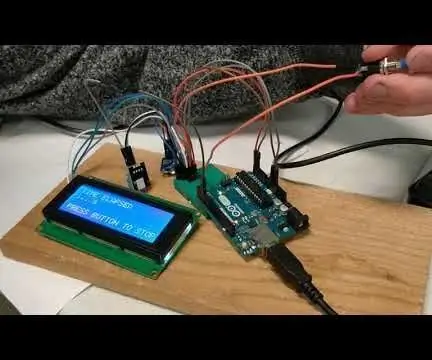

Jam / Jam Randik Arduino Mudah: 6 Langkah (dengan Gambar)

Jam / Jam Randik Arduino Sederhana: Ini " boleh diajar " akan menunjukkan dan mengajar anda cara membuat jam Arduino Uno ringkas yang juga bertindak sebagai jam randik hanya dalam beberapa langkah mudah

Jam Randik Satu Minit VHDL: 5 Langkah

Jam Randik Satu Minit VHDL: Ini adalah tutorial bagaimana membina jam randik satu minit menggunakan VHDL dan papan Basys 3. Peranti sedemikian sesuai untuk permainan di mana setiap pemain mempunyai masa maksimum satu minit untuk bergerak. Jam randik memaparkan detik dan milisaat dengan tepat

Jam Randik VHDL: 8 Langkah (dengan Gambar)

Jam Randik VHDL: Ini adalah tutorial bagaimana membuat jam randik menggunakan VHDL dan papan litar FPGA, seperti Papan Basys3 Atrix-7. Jam randik dapat mengira dari 00.00 saat hingga 99.99 saat. Ia menggunakan dua butang, satu untuk butang mula / berhenti dan satu lagi untuk