Isi kandungan:

- Pengarang John Day [email protected].

- Public 2024-01-30 11:12.

- Diubah suai terakhir 2025-01-23 15:01.

Ini adalah tutorial bagaimana membina jam randik satu minit menggunakan VHDL dan papan Basys 3. Peranti sedemikian sesuai untuk permainan di mana setiap pemain mempunyai masa maksimum satu minit untuk bergerak. Jam randik dengan tepat memaparkan detik dan milisaat pada paparan tujuh segmen, bermula pada 0 saat dan 0 milisaat, hingga 60 saat dan 0 milisaat. Dua butang juga digunakan: butang tengah, digunakan untuk memulakan, menghentikan, dan meneruskan pemasa, dan butang kanan, digunakan untuk menghidupkan semula pemasa. Apabila peranti dibandingkan bersebelahan dengan jam randik terbina dalam telefon pintar, ketepatan jam dapat dilihat.

Langkah 1: Dapatkan Perkakasan / Perisian

1. Basys 3 Artix-7 FPGA Trainer Board dari Digilent dengan Mikro-USB ke Kabel USB

2. Vivado 2016.2 Design Suite dari Xilinx

Langkah 2: Gambarajah Blok

Litar ini dibina secara tingkah laku dan menggunakan komponen Xilinx terbina dalam, tetapi juga dapat dijelaskan secara struktur, seperti yang ditunjukkan oleh gambarajah struktur umum di atas. Dari rajah tersebut, dapat dilihat bahawa litar digerakkan oleh dua pembahagi frekuensi. Salah satu pembahagi frekuensi berjalan pada 1 centisecond dan menggerakkan penghitung katod yang digunakan sebagai nombor yang dipaparkan pada paparan tujuh segmen. Pembahagi frekuensi kedua berjalan pada 240Hz dan digunakan untuk menggerakkan pembilang anod yang berputar melalui anod sehingga semua angka dipaparkan dengan betul pada paparan tujuh segmen. Pengekod mengambil logik katod dari kaunter katod dan logik anod dari kaunter anod, dan menyandikannya ke katod dan anod keluaran yang menjalankan paparan tujuh segmen. Fungsi pengekod ini adalah untuk output katod berubah setiap kali output anod berubah. Output katod tidak dapat dijalankan secara bebas dari pembilang kerana anod mesti berputar melalui 4 digit yang berasingan.

Langkah 3: Modul Projek

Pertama, blok proses untuk CEN dibuat supaya apabila Button Press dikesan, ENABLE akan beralih. Ini berfungsi sebagai penghenti / permulaan kaunter katod.

Pada blok proses seterusnya, isyarat jam sentimeter dan 240Hz ditetapkan supaya pembilang masing-masing meningkat sebanyak 1 setiap kali jam 100mHz dalaman mencapai kenaikan. Setelah pembilang sentimeter mencapai 500000, kaunter akan diset semula ke 0. Sementara itu, kaunter 240Hz akan diset semula apabila kiraannya mencapai 41667.

Untuk bahagian katod kod, jika ENABLE adalah '0' maka penghitungan katod akan berhenti. Sekiranya butang reset ditekan selama ini, maka semua kiraan ditetapkan semula ke "0000". Sementara itu, jika ENABLE adalah '1', pengiraan katod akan berterusan sehingga kiraan katod mencapai 60.00, di mana ia memicu isyarat berhenti menjadi '1'. Isyarat berhenti kembali ke blok proses CEN dan menyebabkan ENABLE menjadi '0' sementara isyarat berhenti adalah '1' dan tidak akan berubah sehingga butang reset ditekan.

Akhirnya, paparan tujuh segmen disiapkan dengan menghubungkan 4 anod dengan 8 katod masing-masing untuk memaparkan digit masing-masing 0-9 secara serentak.

Langkah 4: Kekangan

Fail kekangan ini menghubungkan input dan output yang ditentukan dari VHDL ke bahagian fizikal yang diperlukan dari papan Basys. Untuk projek ini, komponen merangkumi empat anod dan masing-masing lapan katod mereka untuk paparan tujuh segmen, jam 100 mHz dalaman, butang tengah, dan butang kanan.

Langkah 5: Uji

Setelah melengkapkan kod, anda kini dapat memprogram FPGA melalui kabel USB. Paparan tujuh segmen harus menunjukkan 0.00. Uji untuk melihat apakah butang berfungsi dengan menekan butang tengah untuk memulakan pemasa sehingga mencapai 60.00 dan berhenti; bila-bila masa di antara, anda boleh menekan butang tengah sekali lagi untuk menghentikannya. Setelah dijeda, anda boleh menekan butang kanan untuk menetapkan semula pemasa kembali ke 0.00. Sekiranya semuanya berfungsi dengan betul, tahniah anda baru sahaja membina pemasa satu minit!

Disyorkan:

Jam Randik Arduino Leonardo: 3 Langkah

Jam Randik Arduino Leonardo: Kredit: https://www.instructables.com/id/Arduino-Stopwatch..Reka bentuk jam randik ini berasal dari pautan di atas, yang merupakan jam randik yang dihitung dari 1, sedangkan yang ini dihitung dari 60 saat . Sebilangan besar kod yang saya gunakan mengikuti yang asli

Jam Randik Asas Menggunakan Papan VHDL dan Basys3: 9 Langkah

Jam Randik Asas Menggunakan Papan VHDL dan Basys3: Selamat datang di instruksional mengenai cara membina jam randik menggunakan papan asas VHDL dan Basys 3. Kami teruja untuk berkongsi projek kami dengan anda! Ini adalah projek akhir untuk kursus CPE 133 (Digital Design) di Cal Poly, SLO pada Musim Gugur 2016. Projek yang kami bina

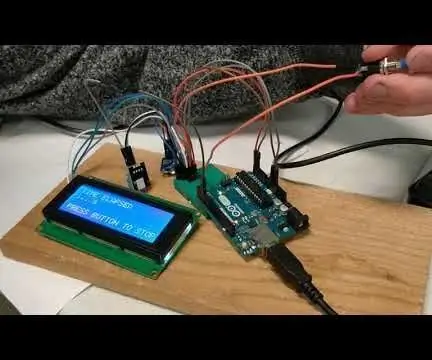

Jam / Jam Randik Arduino Mudah: 6 Langkah (dengan Gambar)

Jam / Jam Randik Arduino Sederhana: Ini " boleh diajar " akan menunjukkan dan mengajar anda cara membuat jam Arduino Uno ringkas yang juga bertindak sebagai jam randik hanya dalam beberapa langkah mudah

Jam Randik VHDL: 8 Langkah (dengan Gambar)

Jam Randik VHDL: Ini adalah tutorial bagaimana membuat jam randik menggunakan VHDL dan papan litar FPGA, seperti Papan Basys3 Atrix-7. Jam randik dapat mengira dari 00.00 saat hingga 99.99 saat. Ia menggunakan dua butang, satu untuk butang mula / berhenti dan satu lagi untuk

Kaedah Sponge + Ferric Chloride - Etch PCB dalam Satu Minit !: 5 Langkah (dengan Gambar)

Kaedah Sponge + Ferric Chloride - Etch PCBs in One Minute !: Dalam instruksional ini, saya akan menunjukkan kepada anda cara membuat papan litar dengan kira-kira satu sudu larutan etsa ferik klorida dan span persegi 2 inci. Anda akan kagum kerana tembaga yang terkena pada PCB hilang di depan mata anda, dan babi hutan anda