Isi kandungan:

- Pengarang John Day day@howwhatproduce.com.

- Public 2024-01-30 11:12.

- Diubah suai terakhir 2025-01-23 15:01.

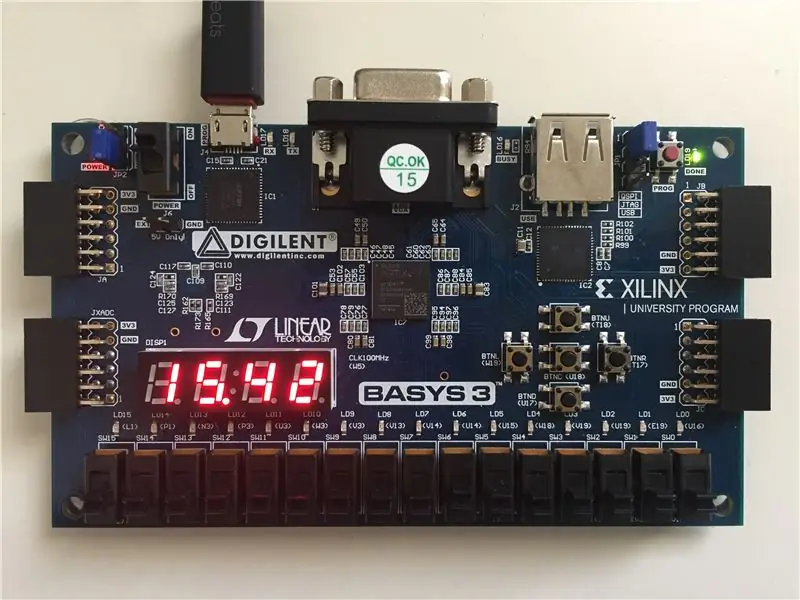

Ini adalah tutorial bagaimana membuat jam randik menggunakan VHDL dan papan litar FPGA, seperti Papan Basys3 Atrix-7. Jam randik dapat mengira dari 00.00 saat hingga 99.99 saat. Ia menggunakan dua butang, satu untuk butang start / stop dan satu lagi untuk butang reset. Angka-angka tersebut dipaparkan pada paparan tujuh segmen papan menggunakan anod dan katodnya. Terdapat tiga fail berbeza yang diperlukan agar jam randik ini berfungsi.

Langkah 1: Perkakasan / Perisian

- Papan Basys3 Atrix-7 FPGA

- Vivado Design Suite dari Xilinx

- USB 2.0 Seorang Lelaki hingga Lelaki Mikro-B

Langkah 2: Gambarajah Blok

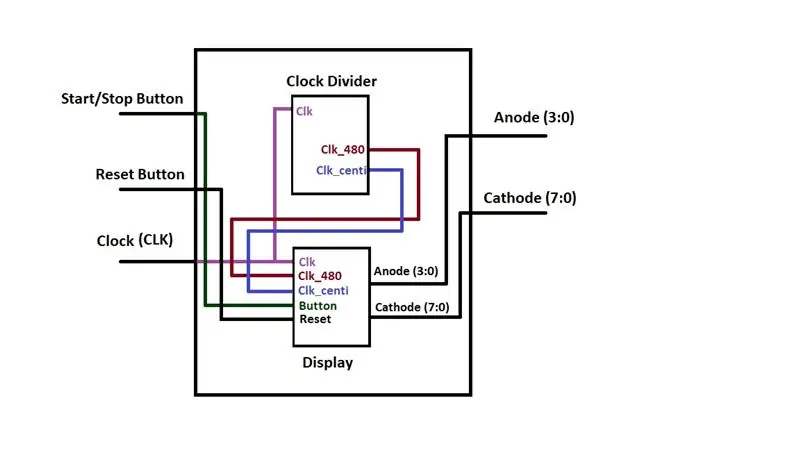

Jam randik keseluruhan mempunyai tiga input dan dua output. Ketiga input tersebut adalah start / stop, reset, dan jam. Mula / berhenti dan menetapkan semula adalah butang dan jam adalah jam 100MHz papan. Dua output adalah anod dan katod untuk paparan tujuh segmen.

Modul pertama (pembahagi jam) mempunyai satu input dan dua output. Input adalah jam 100MHz papan dan outputnya adalah dua jam yang berasingan, satu berjalan pada 480Hz dan satu lagi berjalan 0.5MHz.

Modul kedua (paparan) mempunyai lima input dan dua output. Inputnya adalah jam 100MHz papan, dua jam dari modul pembahagi jam, dan butang mula / berhenti dan set semula. Keluarannya adalah anod dan katod.

Modul terakhir (dimodelkan oleh keseluruhan rajah blok) mempunyai tiga input dan dua output. Ini adalah fail yang menyatukan semuanya. Inputnya adalah 100MHz papan dan butang mula / berhenti dan tetapkan semula. Keluarannya adalah anod dan katod yang mengawal paparan tujuh segmen. Semua input dan output secara fizikal berada di papan untuk modul akhir.

Langkah 3: Rajah Negeri

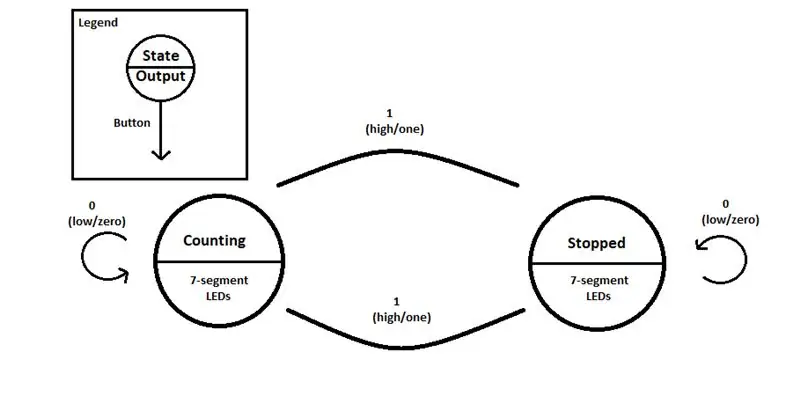

Gambar di atas menunjukkan gambarajah keadaan bagaimana jam randik berfungsi. Menekan butang reset tidak mempengaruhi keadaan jam randik. Keadaan seterusnya ditentukan oleh butang mula / berhenti. Permulaan / berhenti adalah "TINGGI" ketika ditekan ke bawah, tetapi tidak ketika ditekan ke bawah, dan "RENDAH" apabila butang itu kembali melantun atau ditahan setelah "TINGGI" sesaat.

Sekiranya jam randik dihitung dan butang mula / berhenti menjadi "TINGGI", maka ia berhenti mengira. Sekiranya jam randik dihentikan dan butang mula / berhenti menjadi "TINGGI" maka ia mula dikira lagi. Untuk kedua-dua keadaan, jika butang mula / henti adalah "RENDAH", maka ia akan tetap berada dalam keadaan di mana ia berada sekarang.

Langkah 4: Modul Pembahagi Jam

Modul pembahagi jam mempunyai satu input, jam 100MHz papan, dan dua output, jam 480Hz dan 0.5MHz. Jam 480Hz digunakan untuk memastikan semua LED pada paparan tujuh segmen "menyala" pada masa yang sama dengan beralih ke empat dengan pantas. Jam 0.5MHz digunakan untuk jam randik benar-benar dihitung dengan senti-saat.

Langkah 5: Modul Paparan

Modul paparan ini mempunyai lima input, jam 100MHz papan, dua jam dari modul jam, dan butang mula / berhenti dan set semula, dan dua output, anod dan katod. Modul ini juga mempunyai "logik" untuk bagaimana jam randik mengira dan menggabungkan mesin keadaan terhingga.

Langkah 6: Modul Mengikat

Modul terakhir ini adalah satu yang menyatukan dua modul yang lain. Ia mempunyai tiga input, jam 100MHz papan dan butang start / stop and reset, dan dua output, anod dan katod. Jam 100MHz menuju ke modul pembahagi jam dan modul paparan, dan butang mula / berhenti dan set semula masuk ke modul paparan. Keluaran modul pembahagi jam (480Hz dan 0.5MHz) menuju ke input dua jam dari modul paparan. Keluaran modul paparan (anod dan katod) menuju ke output modul akhir.

Langkah 7: Kekangan

Kedua-dua input boleh menjadi sebarang butang pada Papan FPGA Basys3 Atrix-7 dan outputnya akan menjadi empat anod dan lapan katod (kerana anda juga mahukan titik perpuluhan antara saat dan milisaat) untuk paparan tujuh segmen.

Langkah 8: Selesai

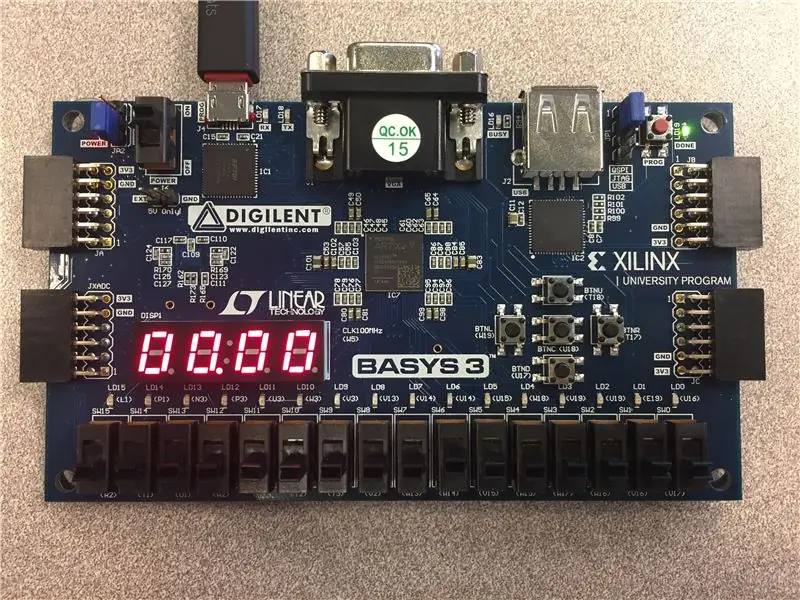

Muat naik program ke Papan FPGA Basys3 Atrix-7 anda dan tekan butang mula / berhenti anda untuk mendapatkan jam randik!

Disyorkan:

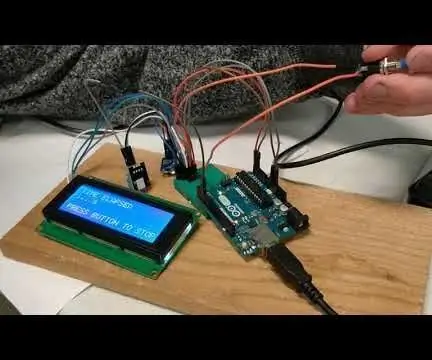

Cara Membuat Jam Randik Menggunakan Arduino: 8 Langkah (dengan Gambar)

Cara Membuat Jam Randik Menggunakan Arduino: Ini Jam Ringkas Paparan Arduino 16 * 2 Lcd Yang Sangat Sederhana ……….. Sekiranya Anda Suka Ini Boleh Diperintahkan Sila Langgan Saluran Saya https://www.youtube.com / ZenoModiff

Jam Randik Asas Menggunakan Papan VHDL dan Basys3: 9 Langkah

Jam Randik Asas Menggunakan Papan VHDL dan Basys3: Selamat datang di instruksional mengenai cara membina jam randik menggunakan papan asas VHDL dan Basys 3. Kami teruja untuk berkongsi projek kami dengan anda! Ini adalah projek akhir untuk kursus CPE 133 (Digital Design) di Cal Poly, SLO pada Musim Gugur 2016. Projek yang kami bina

Jam Randik Arduino: 4 Langkah (dengan Gambar)

Arduino Stopwatch: Instructable ini akan menunjukkan kepada anda cara membuat stopwatch dari Arduino

Jam / Jam Randik Arduino Mudah: 6 Langkah (dengan Gambar)

Jam / Jam Randik Arduino Sederhana: Ini " boleh diajar " akan menunjukkan dan mengajar anda cara membuat jam Arduino Uno ringkas yang juga bertindak sebagai jam randik hanya dalam beberapa langkah mudah

Jam Randik Satu Minit VHDL: 5 Langkah

Jam Randik Satu Minit VHDL: Ini adalah tutorial bagaimana membina jam randik satu minit menggunakan VHDL dan papan Basys 3. Peranti sedemikian sesuai untuk permainan di mana setiap pemain mempunyai masa maksimum satu minit untuk bergerak. Jam randik memaparkan detik dan milisaat dengan tepat