Isi kandungan:

- Langkah 1: Operasi Pengguna Sequencer Digital

- Langkah 2: Butiran Teknikal

- Langkah 3: Butiran Teknikal

- Langkah 4: Pembahagi Jam 7 segmen

- Langkah 5: Beats Per Minute Clider Pembahagi

- Langkah 6: Pitches Clock Divider

- Langkah 7: Main / Jeda / Pilih Mesin Negeri

- Langkah 8: Main / Jeda / Pilih Mesin Negeri

- Langkah 9: Output FSM

- Langkah 10: Output FSM

- Langkah 11: Tugaskan Catatan

- Langkah 12: Pilih Hasil

- Langkah 13: Gen Gelombang Persegi

- Langkah 14: Paparan 7 segmen

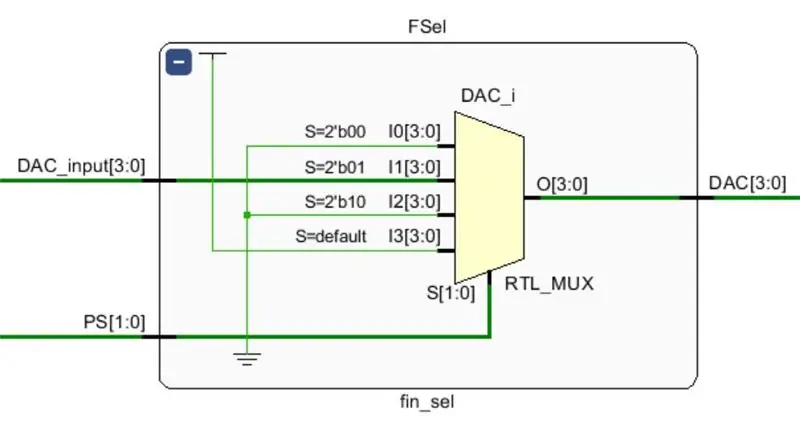

- Langkah 15: Pilih Akhir

- Langkah 16: Peranti Luaran: DAC

- Langkah 17: Peranti Luaran: Pembesar suara

- Langkah 18: Demo Video

- Langkah 19: Kod VHDL

- Pengarang John Day day@howwhatproduce.com.

- Public 2024-01-30 11:12.

- Diubah suai terakhir 2025-01-23 15:01.

CPE 133, Cal Poly San Luis Obispo

Pencipta Projek: Jayson Johnston dan Bjorn Nelson

Dalam industri muzik masa kini, salah satu "instrumen" yang paling biasa digunakan adalah synthesizer digital. Setiap genre muzik, dari hip-hop hingga pop dan bahkan negara, menggunakan synthesizer digital di studio untuk membuat rentak dan suara yang mereka perlukan untuk menghidupkan muzik mereka. Dalam tutorial ini, kita akan membuat synthesizer yang sangat mudah dengan papan Basys 3 FPGA.

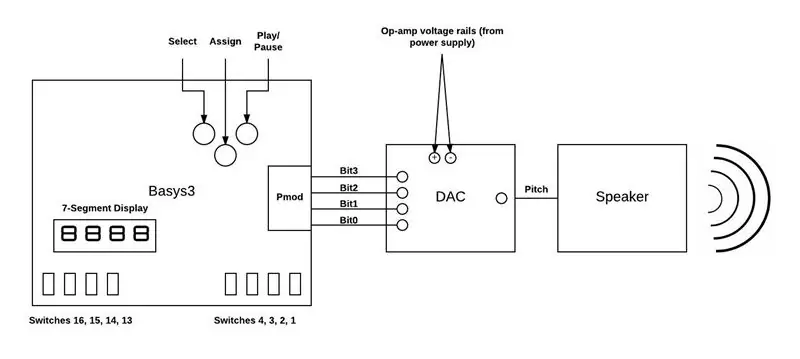

Synthesizer akan dapat memainkan empat nota suku terpilih dengan jumlah rentak berterusan setiap minit. Pengguna akan menggunakan suis untuk menetapkan setiap nota suku ke nada muzik. Untuk projek ini, kami menggunakan penukar digital ke analog 4-bit (DAC) untuk mengambil output dari papan dan menukarnya menjadi isyarat analog. Output dari DAC kemudian akan dimasukkan ke pembesar suara komputer standard, mencipta muzik kami. Enam belas nada diskrit mungkin. Kami akan menghadkan synthesizer kami kepada oktaf tunggal sebanyak 12 nota, yang berada di antara C tengah (261.6 Hz) dan B4 (493.9 Hz). Pengguna juga akan mempunyai pilihan untuk memberikan beberapa nota pada masa yang sama, serta memberikan rehat dengan memukul assign sambil tidak ada satu pun suis pitch yang beralih ke atas. Oleh kerana setiap nota dipilih dan dimainkan, nota huruf ditunjukkan pada paparan 7 segmen. Kami juga akan menggunakan tiga tombol di papan tulis, satu untuk bermain dan menjeda muzik, satu untuk mengatur ulang synthesizer dan memasukkannya ke dalam mod "pilihan", dan yang ketiga untuk menetapkan nada setiap nada ketika berada dalam mode pilihan.

Setelah pengguna berpuas hati dengan pilihan nota mereka, dan setelah menekan butang main, synthesizer akan memainkan setiap not berturut-turut sehingga pengguna sama ada menekan jeda atau memilih.

Berikut adalah senarai peralatan yang diperlukan:

- Vivado (atau mana-mana ruang kerja VHDL)

- Basys 3 atau papan FPGA yang serupa

- Penukar digital ke analog (min. 4-bit)

- Pembesar suara dengan bicu fon kepala

- Dawai wayar

Langkah 1: Operasi Pengguna Sequencer Digital

Langkah-langkah berikut adalah mengoperasikan penjujukan digital. Penjujukan digital menyokong pemutaran 12 nada berbeza (C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B), yang berkisar antara 261.6 Hz hingga 493.9 Hz.

1. Tekan butang kiri untuk memasukkan papan ke mod pilihan. Ketika berada dalam mod ini, 4 suis paling kiri (suis 13 hingga 16) masing-masing akan digunakan untuk menyimpan nilai nada yang berbeza.

2. Untuk membuat pilihan, putar salah satu suis kiri, dan kemudian gunakan 4 suis paling kanan (suis 1 hingga 4) untuk memilih nada yang diinginkan. Nada suara yang dikaitkan dengan kombinasi suis kanan tertentu akan ditunjukkan pada paparan tujuh segmen, dan layar akan diperbarui ke nada terkait baru setiap kali suis kanan dialihkan ke kombinasi baru. Rehat dapat diberikan dengan tidak pernah memberikan nada ke salah satu suis kiri, atau dengan menetapkan nada yang ditunjukkan sebagai 0 pada paparan pada nota. Setelah nada yang diinginkan dijumpai dan ditunjukkan pada paparan, tekan butang tetapkan bawah untuk menetapkan nada tertentu itu ke nota.

3. Ulangi langkah 2 untuk tiga nota yang tinggal, dengan membalikkan setiap suis kiri yang tersisa secara berasingan, memilih nada masing-masing dengan suis kanan, dan menekan butang bawah untuk menetapkan nada ke nota. Beberapa nota dapat diberikan nada yang sama dengan menggeser lebih dari satu suis kiri ke atas pada masa yang sama.

4. Setelah semua nada nota telah ditetapkan, penjujukan digital sudah siap dimainkan. Untuk memainkan nota pada pembesar suara, tekan butang putar / jeda kanan untuk mula memainkan muzik. Urutan urutan main balik mencerminkan nada yang berkaitan dengan suis kiri, dari kiri ke kanan. Nota akan dimainkan pada jumlah rentak per minit, mengikut urutan 1, 2, 3, 4, 1, 2…. Paparan akan menunjukkan nota yang sedang dimainkan semasa pembesar suara memainkan muzik. Untuk menjeda pemutaran muzik, cukup tekan butang kanan, dan kemudian muzik akan berhenti diputar dan simbol jeda akan ditunjukkan di layar. Menekan butang kanan sekali lagi akan menyambung main semula.

Langkah 2: Butiran Teknikal

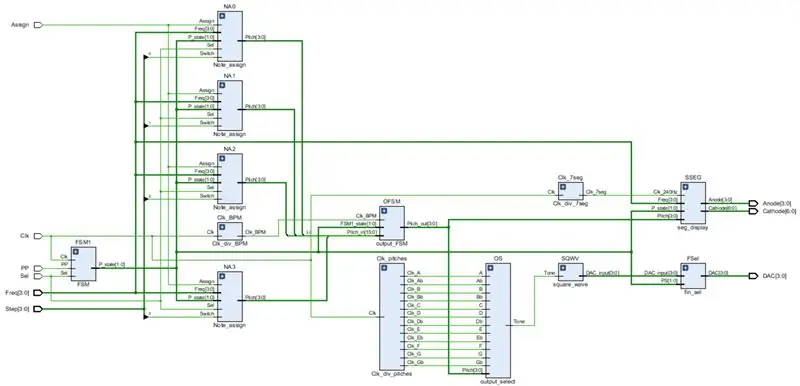

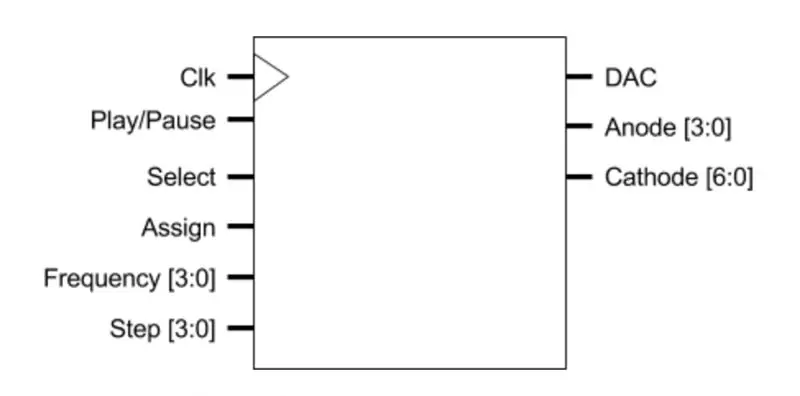

Synthesizer kami menggunakan banyak komponen digital yang berbeza. Termasuk mesin keadaan terhingga, daftar, multiplexer, pembahagi jam dan banyak lagi. Untuk membina synthesizer kami, kami menggunakan 10 fail modular yang unik. Daripada menjadikan setiap modul sebagai komponen, kami memecahkan fail modular mengikut fungsi. Oleh itu, kebanyakan modul adalah lebih daripada satu komponen. Perhatikan gambar di atas menunjukkan setiap blok terikat dalam reka bentuk teratas kami.

Kami akan membincangkan setiap modul dengan menerangkan input dan output, menguraikan komponennya, dan menjelaskan tujuannya dalam reka bentuk keseluruhan. Fail ZIP disertakan di bahagian bawah arahan, yang mengandungi setiap fail kod VHDL yang digunakan dalam projek.

Input

- Clk (isyarat jam asli)

- PP (main / jeda)

- Sel (masukkan synthesizer dalam mod pilihan)

- Tugaskan (berikan langkah ke nada)

- Langkah (nota kedudukan)

- Freq (suis mencipta nada yang diinginkan)

Keluaran

- Anod (anod 7 segmen)

- Katod (katod 7 segmen)

- DAC (4-bit memandu DAC)

Langkah 3: Butiran Teknikal

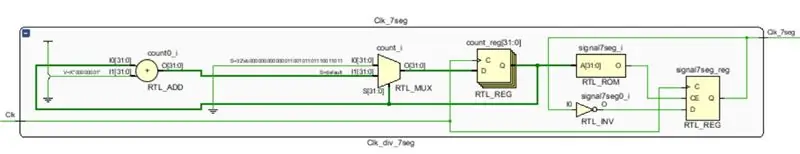

Langkah 4: Pembahagi Jam 7 segmen

Synthesizer kami menggunakan tiga pembahagi jam, semuanya menghasilkan isyarat yang berfungsi dengan tujuan yang berbeza dalam projek kami. Pembahagi jam mengambil isyarat jam asli dan menghasilkan isyarat yang diubah yang mempunyai frekuensi kurang daripada isyarat jam asal. Jam asli Basys 3 ialah 100 MHz. Ini adalah kekerapan yang digunakan oleh pembahagi jam kami. Sekiranya anda menggunakan papan FPGA yang berbeza dengan frekuensi jam asli yang berbeza, anda mungkin perlu mengubah kodnya.

Pembahagi jam 7 segmen menghasilkan isyarat yang mendorong fail paparan seg_. Kami akan menerangkan bagaimana fail ini berfungsi dengan lebih terperinci apabila kami sampai ke bahagiannya. Pada dasarnya, pembahagi jam ini menghasilkan isyarat 240 Hz yang akan digunakan untuk menukar antara anod dan katod pada paparan. Isyaratnya ialah 240 Hz kerana frekuensi di mana mata manusia tidak dapat mengenali ketiadaan cahaya adalah 60 Hz. Kami menggunakan dua digit, jadi dengan menggandakan frekuensi ini, setiap digit akan berayun pada 60 Hz. Kemudian kita menggandakannya sehingga mendapat 240 Hz kerana sistem hanya berubah ketika isyarat naik tinggi, bukan ketika rendah.

Untuk mencapainya, pembahagi mengambil isyarat asli 100 MHz dan mengira setiap sisi yang meningkat. Apabila kaunter mencapai 416667, output akan turun dari rendah ke tinggi, atau sebaliknya.

Input

Clk (isyarat jam asli)

Keluaran

Clk_7seg (ke seg_display)

Komponen

- D daftar

- MUX

- Penyongsang

- Penambah

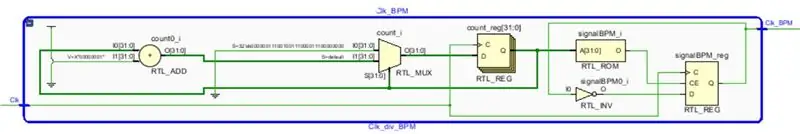

Langkah 5: Beats Per Minute Clider Pembahagi

Pembahagi jam BPM berfungsi dengan cara yang serupa. Pembahagi ini menghasilkan frekuensi jam yang mendorong pertukaran antara empat langkah ketika mengeluarkan nada dalam keadaan bermain. Kami memutuskan untuk menukar antara nota pada 100 BPM. Pada 100 BPM, setiap nota akan dimainkan selama 3/5 saat. Isyarat yang dihasilkan akan mempunyai frekuensi 1.67 Hz.

Untuk menghasilkan isyarat frekuensi ini, kami sekali lagi menggunakan sistem penghitungan, tetapi kali ini jumlahnya 60 juta. Setiap kali kaunter mencecah 60 juta, isyarat output akan beralih tinggi atau rendah.

Input

Clk (kekerapan jam asli)

Keluaran

Clk_BPM (ke output_FSM)

Komponen

- D daftar

- MUX

- Penyongsang

- Penambah

Langkah 6: Pitches Clock Divider

Pitches Clock Divider adalah pembahagi jam terbesar. Pembahagi ini mengeluarkan 12 isyarat berbeza yang sesuai dengan 12 nota berbeza yang boleh dimainkan oleh synthesizer kami. Dengan menggunakan pengetahuan asas teori muzik, kami menyimpulkan bahawa sedikit atau bas dapat berayun pada kadar yang sesuai dengan frekuensi nota muzik. Untuk melihat frekuensi yang kami gunakan, lihat di sini. Kami menggunakan lapan oktaf keempat.

Sistem pengiraan yang sama digunakan di sini. Untuk nilai tertentu yang kami hitung, lihat fail berlabel Clk_div_pitches.

Input

Clk (kekerapan jam asli)

Keluaran

C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B (untuk output_select)

Komponen

- D daftar

- MUX

- Penyongsang

- Penambah

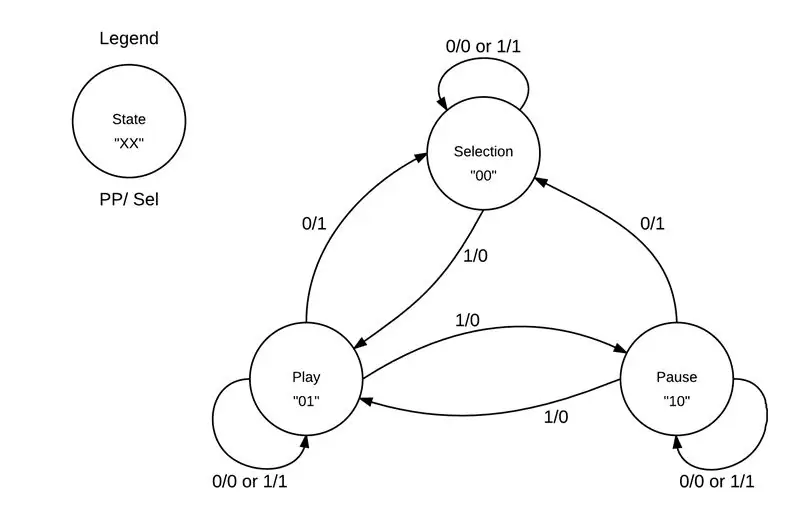

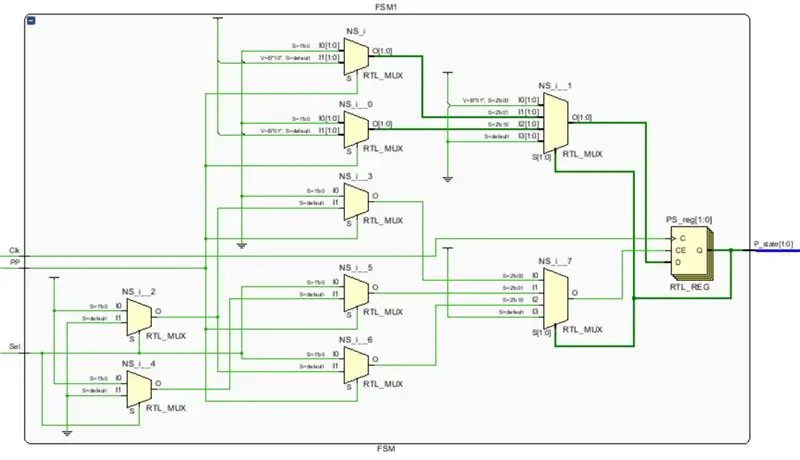

Langkah 7: Main / Jeda / Pilih Mesin Negeri

Dalam projek kami terdapat dua mesin keadaan terhingga (FSM). FSM adalah peranti logik yang boleh wujud hanya dalam satu keadaan daripada jumlah keadaan yang terhad. Dengan menggunakan FSM, litar digital dapat bergerak ke keadaan baru berdasarkan gabungan input. Dengan menggunakan logik input, keadaan FSM akan berubah apabila terdapat kelebihan jam. Dari keadaan dan input ke litar, anda boleh membuat logik output yang memberikan output yang hanya ada jika FSM berada dalam keadaan tertentu.

Mesin keadaan PPS adalah FSM pertama di litar kami. Terdapat tiga negeri di FSM ini; Mod Main, Jeda, dan Pilihan. Untuk bergerak melalui keadaan yang berbeza, kami menggunakan butang PP dan Pemilihan. Lihat rajah keadaan di atas untuk melihat bagaimana peralihan antara keadaan berlaku. Kami membuat peralihan FSM ini di hujung jam 100 MHz asli, sehingga tidak mungkin mesin tidak beralih ketika salah satu butang ditekan, walaupun untuk waktu yang sangat singkat. Keadaan sekarang (P_state) adalah satu-satunya output dari modul ini.

Input

- Clk (kekerapan jam asli)

- Sel (butang kiri)

- PP (butang kanan)

Keluaran

P_state (keadaan sekarang, ke output_FSM, note_assign, seg_dsiplay, final_select)

Komponen

- MUX

- D daftar

Langkah 8: Main / Jeda / Pilih Mesin Negeri

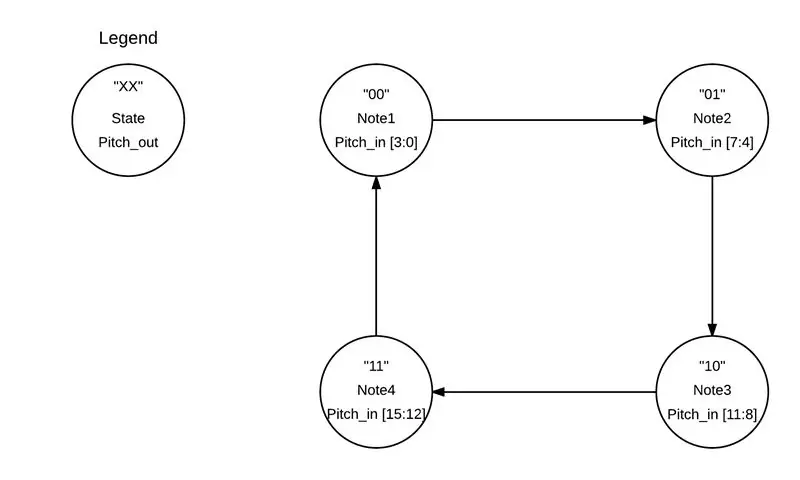

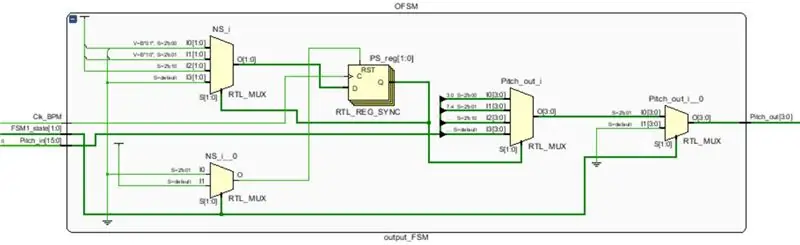

Langkah 9: Output FSM

Ini adalah FSM kedua yang dirujuk pada bahagian sebelumnya. FSM ini berfungsi dengan fungsi yang berbeza daripada yang lain, tetapi asas untuk ini pada dasarnya sama.

FSM keluaran hanya beroperasi jika keadaan sekarang dari FSM pertama adalah "01" (keadaan main). Pada asasnya, ini adalah kemampuan masuk untuk modul. Sekiranya keadaan adalah "01", maka FSM akan beralih antara keadaan di tepi isyarat jam BPM yang semakin meningkat. Kami melakukan ini kerana output_FSM mengawal nombor binari mana untuk nada yang dipilih dihantar ke modul output_select dan seg_display. FSM mempunyai input 16-bit yang berasal dari modul pemberian nota, yang akan dibahas seterusnya. Dalam keadaan "00" untuk output_FSM, modul akan mengeluarkan "xxxx" untuk nota pertama yang diberikan. Kemudian pada "01", ia akan mengeluarkan "yyyy" untuk nota kedua dan seterusnya untuk setiap nota sebelum kembali ke nota pertama. Lihat gambarajah keadaan di atas.

FSM ini berbeza dari yang pertama kerana tidak ada logik input untuk mengawal pertukaran antara keadaan. Sebaliknya, FSM hanya akan beroperasi apabila keadaan dari FSM pertama adalah "01", dan kemudian FSM ini akan beralih antara keadaan hanya di tepi isyarat jam yang meningkat. Perbezaan lain ialah modul ini mempunyai logik output, yang bermaksud tidak mengeluarkan keadaan sekarang, ia mengeluarkan nombor binari untuk nada pada keadaan tersebut.

Input

- Clk_BPM (isyarat jam BPM dari pembahagi jam)

- FSM1_state (PS dari PPS FSM)

- Pitch_in (nada dari note_assign)

Keluaran

Pitch_out (satu nada pada satu waktu, untuk output_select dan seg_display)

Komponen

- MUX

- D daftar

Langkah 10: Output FSM

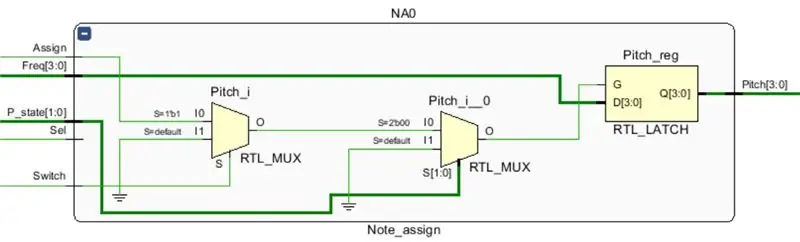

Langkah 11: Tugaskan Catatan

Modul pemberian nota bertanggungjawab untuk benar-benar memberikan nada ke nota kedudukan, atau langkah. Modul ini sebenarnya agak mudah. Mula-mula memeriksa apakah litar berada dalam keadaan "pilihan" dan apakah suis langkah (kiri paling tinggi) tinggi. Sekiranya ini benar dan butang penugasan ditekan, output modul akan sama dengan nombor binari yang ditunjukkan oleh suis frekuensi (paling kanan).

Pada asalnya, kami telah berusaha membuat modul yang sebenarnya dapat menyimpan salah satu isyarat jam nada ke output, tetapi kami mengalami masalah dengan output yang berubah untuk mengikuti isyarat jam input. Ini adalah satu-satunya modul yang digunakan lebih daripada sekali dalam reka bentuk akhir. Setiap langkah mempunyai modul note_assign yang berkaitan dengannya, dan kerana itu, setiap contoh modul mendapat sedikit dari langkah Step.

Input

- P_state (keadaan sekarang dari PPS FSM)

- Sel (butang kiri)

- Suis (suis satu langkah)

- Freq (suis paling kanan untuk nada)

- Tetapkan (butang bawah, berikan nota)

Keluaran

Pitch (nombor perduaan, ke output_FSM)

Komponen

- MUX

- D mendaftar semula

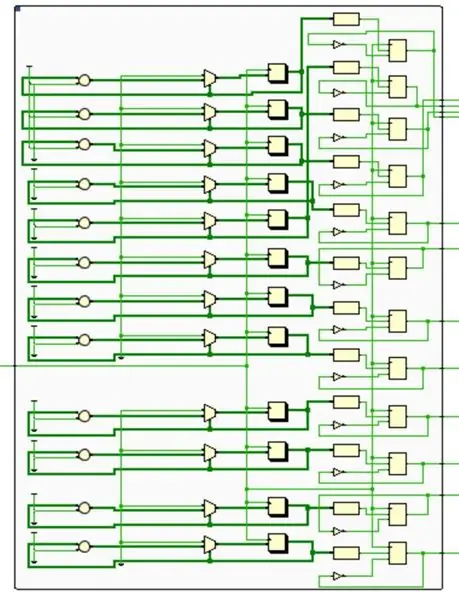

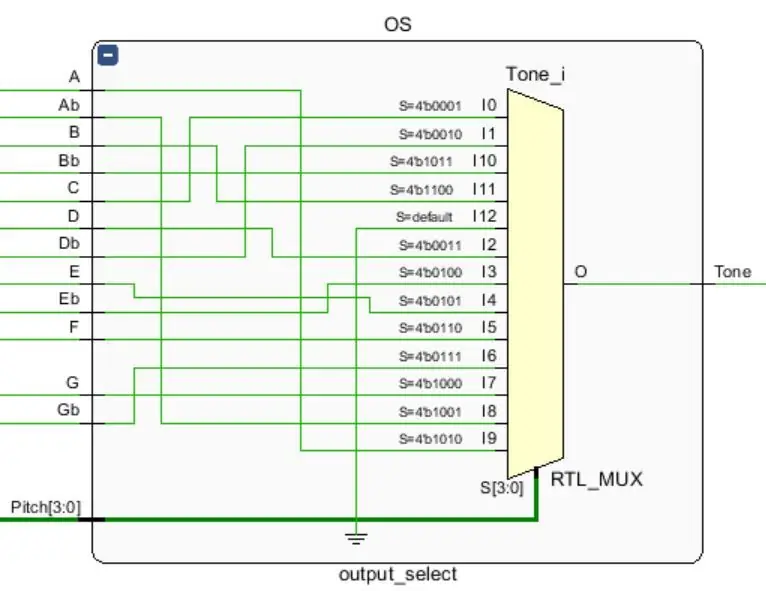

Langkah 12: Pilih Hasil

Pilihan output bertanggungjawab untuk mengambil nombor binari untuk nada dan menghubungkannya ke isyarat jam masing-masing. Walaupun ukurannya, ini juga merupakan modul yang agak mudah. Output_select pada dasarnya adalah penyahkod binari, menyahkod nombor binari untuk nada ke isyarat jam tertentu. Sebenarnya menetapkan output ke frekuensi jam berfungsi lebih baik di sini berbanding modul note_assign, kerana semua modul ini harus dilakukan adalah MUX isyarat jam dengan nombor binari yang mewakili input kawalan.

Kami meminta maaf atas peralihan yang aneh, Vivado mengatur isyarat nada mengikut abjad untuk fail clk_div_pitches, tetapi untuk fail ini, ia mengaturnya dengan menaikkan nombor binari, menyebabkan nada berada dalam urutan yang berbeza. Juga perhatikan bahawa jika nombor binari dari output_FSM adalah "0000" atau apa-apa yang lebih besar daripada "1100", maka MUX dihantar melalui isyarat '0' rata.

Masukan

- Pitch (dari output_FSM);

- C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B (isyarat jam nada)

Pengeluaran

Nada (satu bit yang sepadan dengan isyarat jam yang dipilih, ke gelombang_jadi)

Komponen

MUX

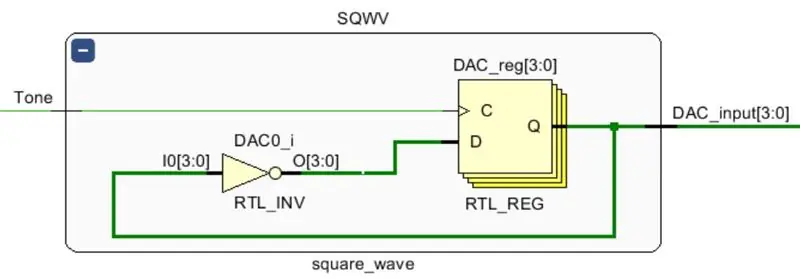

Langkah 13: Gen Gelombang Persegi

Modul square_wave adalah penjana untuk gelombang persegi yang dikeluarkan dari papan ke DAC. Dengan menggunakan isyarat nada dari fail sebelumnya, gelombang persegi_ ini membalikkan nombor 4 bit antara "0000" dan "1111" di pinggir Nada yang semakin meningkat. Nada adalah frekuensi nada tertentu, jadi gelombang_ gelombang menghasilkan gelombang dengan frekuensi yang berbeza ketika output_FSM beralih ke keadaan lain. Output 4-bit dari modul ini menuju ke modul fin_sel, di mana logik menentukan sama ada bas ini akan dikeluarkan berdasarkan keadaan dari PPS FSM.

Alternatif untuk penjana gelombang persegi ini adalah menghasilkan gelombang sinus. Walaupun ini kemungkinan menghasilkan nada akhir yang lebih baik, jauh lebih sukar untuk dilaksanakan, jadi kami memilih untuk hanya menghasilkan gelombang persegi.

Input

Nada (bit berayun dari output_select)

Keluaran

DAC_input (bas 4-bit berayun yang berubah pada frekuensi nada yang sama)

Komponen

- Penyongsang

- D daftar

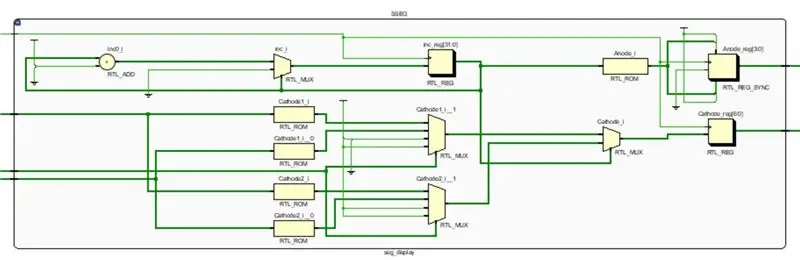

Langkah 14: Paparan 7 segmen

Modul seg_display mengawal paparan 7 segmen di papan dasar kami. Di dalam modul, dua proses berlaku. Proses pertama menyahkod Freq ketika dalam keadaan "pilihan" atau Pitch ketika dalam mod "main". Dalam mod "jeda", modul menyahkod untuk menunjukkan simbol jeda. Melihat kod VHDL, anda dapat melihat bahawa penyahkod binari sebenarnya menyahkod input menjadi dua isyarat yang berbeza, katod1 dan katod2. Cathode1 mewakili huruf yang sesuai dengan nada yang akan ditampilkan, dan katod2 mewakili simbol rata (b) jika ada. Sebabnya ini berkaitan dengan proses kedua yang dilakukan oleh modul seg_display.

Pada papan basys3, paparan segmen mempunyai katod biasa. Semasa anod mengawal digit mana yang dihidupkan, katod mengawal segmen yang dihidupkan. Oleh kerana paparan mempunyai katod umum, itu bermakna anda hanya dapat menampilkan satu set segmen pada satu masa. Ini menimbulkan masalah untuk projek ini kerana kami ingin memaparkan huruf pada digit pertama dan simbol rata, jika perlu, pada masa yang sama. Sekarang ingat isyarat jam 7seg? Untuk mengatasi masalah ini, kami menukar anod dan katod berulang-ulang pada isyarat jam 7seg. Kerana isyarat jam adalah 240 Hz dan kami menggunakan dua digit, setiap digit akan berayun pada 60 Hz. Untuk mata manusia, ia kelihatan seperti digit tidak berayun sama sekali.

Perhatikan juga bahawa paparan papan basys3 menggunakan logik negatif. Ini bermaksud jika anod atau katod ditetapkan ke '0', digit atau segmen tersebut akan dihidupkan, dan sebaliknya.

Input

- Pitch (nombor perduaan untuk nota, digunakan dalam keadaan bermain)

- Freq (suis frekuensi, digunakan ketika berada dalam keadaan pemilihan)

- P_state (keadaan sekarang dari PPS FSM)

- Clk_240Hz (isyarat jam dari Clk_div_7seg, dua kali ganda 120 kerana kita hanya menggunakan kelebihan naik)

Keluaran

- Cathode (bas yang mengawal segmen pada paparan, output akhir)

- Anode (bas yang mengawal digit pada paparan, output akhir)

Komponen

- Selak

- MUX

- D daftar

Langkah 15: Pilih Akhir

Pilihan terakhir adalah modul terakhir yang digunakan dalam projek ini. Modul mudah lain, modul ini mengawal output akhir yang akan menuju ke DAC. Ketika dalam keadaan "seleksi" atau "jeda", modul akan mengeluarkan "0000" statis sehingga tidak akan dimainkan muzik dari pembesar suara. Dalam keadaan "mainkan", modul akan menghasilkan 4-bit berayun seperti yang ditentukan oleh gelombang_jadi.

Input

- P_state (keadaan sekarang dari PPS FSM)

- DAC_input (4-bit berayun dari square_wave)

Keluaran

DAC (sama dengan DAC_input dalam keadaan bermain, output akhir)

Komponen

MUX

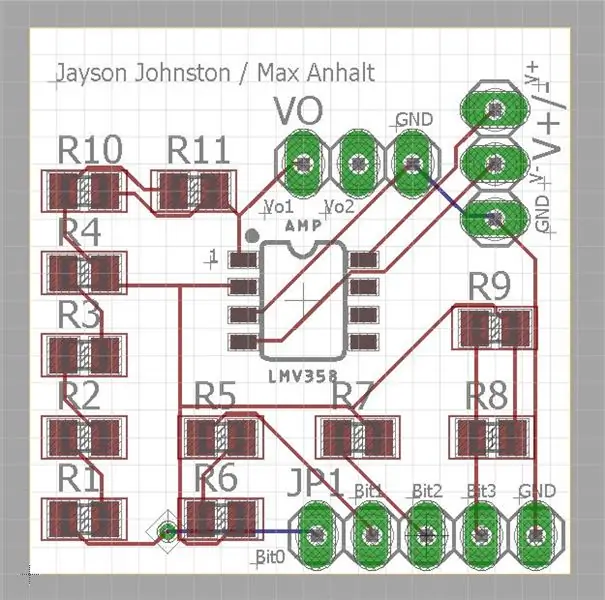

Langkah 16: Peranti Luaran: DAC

Penukar digital ke analog (DAC) mengambil isyarat diskrit dan menukarnya menjadi isyarat berterusan. DAC kami mempunyai empat bit dan dibuat dari penguat penjumlahan. Dengan menggunakan nisbah perintang dalam gelung bekalan dan maklum balas, kami dapat membuat sistem yang menghasilkan pada 16 tahap yang berbeza yang dibuat dengan "penjumlahan" setiap cabang. Bit0, cabang teratas, mempunyai berat paling sedikit dan menyumbang potensi terkecil apabila tinggi kerana rantaian itu mempunyai daya tahan yang lebih tinggi. Berat meningkat semasa anda turun ke dahan. Sekiranya anda mengira secara binari ke atas dan kemudian turun menggunakan input bit, voltan keluaran akan kelihatan seperti gelombang sinus langkah. Input ke DAC disambungkan ke salah satu PMOD di papan untuk memindahkan isyarat 4-bit.

DAC pada asalnya dipasang untuk kelas Kejuruteraan Elektrik dan dirancang dan disolder oleh kami, bukan dibeli dari kedai. Di atas adalah gambar fail reka bentuk untuk membuat papan litar bercetak.

Langkah 17: Peranti Luaran: Pembesar suara

Untuk projek ini, anda tidak akan mahu membeli sepasang pembesar suara yang sangat bagus. Seperti yang anda tahu, suaranya cukup mendasar. Kami pergi dan membeli set pembesar suara komputer bernilai $ 8 dari Best Buy. Apa-apa sahaja dengan bicu fon kepala berfungsi dengan baik. Monoton berfungsi dengan baik juga. Anda bahkan boleh menggunakan fon kepala, tetapi mungkin mengeluarkannya!

Untuk menyambungkan output DAC ke pembesar suara, kami menggunakan kabel jumper dan kemudian memegang kabel output ke hujung bicu fon kepala dan kabel untuk ground ke dasar. Kami cuba menggunakan pita elektrik untuk menahan kabel di tempatnya, tetapi ia menyebabkan banyak gangguan. Mencuba gaya pita yang berbeza dapat menyelesaikan masalah ini.

Untuk pembesar suara kami, kami mengubahnya ke kedudukan tertinggi dan mendapat bunyi yang kuat.

Dan itu adalah langkah terakhir untuk membuat penjujukan digital dari papan FPGA! Pergi ke dua bahagian seterusnya untuk memuat turun semua kod VHDL kami dan melihat penjujukannya beraksi.

Langkah 18: Demo Video

Video ini menunjukkan versi akhir projek yang berfungsi, termasuk proses menetapkan suis ke 4 nada yang berbeza, dan pembesar suara memainkan nota masing-masing.

Langkah 19: Kod VHDL

Berikut adalah kod untuk keseluruhan projek, termasuk kekangan dan fail sim yang digunakan semasa membina jujukan. Perhatikan bahawa fail reka bentuk yang tidak digunakan mengatakan demikian dalam seni bina.

Disyorkan:

Penjejak GPS DIY --- Aplikasi Python: 5 Langkah (dengan Gambar)

DIY GPS Tracker --- Aplikasi Python: Saya mengambil bahagian dalam acara berbasikal dua minggu yang lalu. Setelah selesai, saya ingin memeriksa laluan dan kelajuan yang saya naiki ketika itu. Malangnya, ia tidak dapat dicapai. Sekarang saya menggunakan ESP32 untuk membuat pelacak GPS, dan saya akan mengambilnya untuk merakam laluan berbasikal saya

Kerusi Roda Kendali Joystick Dibantu Dengan Penjejak Halangan: 3 Langkah (dengan Gambar)

Kerusi Roda Joystick Terkawal Dibantu Dengan Penjejak Halangan: Untuk memudahkan orang kurang upaya fizikal dengan selamat menunggang sensor ultrasonik digunakan untuk mengesan rintangan yang ada dalam perjalanan. Berdasarkan pergerakan kayu bedik motor akan memandu kerusi roda dalam empat arah dan kelajuan pada setiap

Membina Penjejak Solar Automatik Dengan Arduino Nano V2: 17 Langkah (dengan Gambar)

Membina Penjejak Solar Automatik Dengan Arduino Nano V2: Hai! Instructable ini dimaksudkan untuk menjadi bahagian kedua dari projek Solar Tracker saya. Untuk penjelasan mengenai bagaimana pelacak solar berfungsi dan bagaimana saya merancang pelacak pertama saya, gunakan pautan di bawah. Ini akan menawarkan konteks untuk projek ini.https: //www.instructables.co

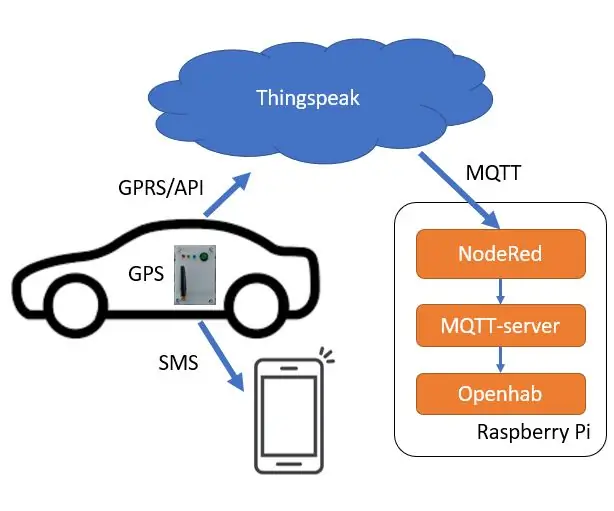

Penjejak Kereta GPS Dengan Pemberitahuan SMS dan Muat Naik Data Perkara, Berbasis Arduino, Automasi Rumah: 5 Langkah (dengan Gambar)

Penjejak Kereta GPS Dengan Pemberitahuan SMS dan Muat Naik Data Thingspeak, Berasaskan Arduino, Automasi Rumah: Saya membuat pelacak GPS ini tahun lalu dan kerana ia berfungsi dengan baik, saya menerbitkannya sekarang di Instructable. Ia disambungkan ke palam aksesori di bagasi saya. Penjejak GPS memuat naik kedudukan kereta, kelajuan, arah dan suhu yang diukur melalui data mudah alih

Penjejak Suria Miniatur DIY: 5 Langkah (dengan Gambar)

DIY Miniature Solar Tracker: Dalam projek ini saya akan menunjukkan kepada anda bagaimana membuat solar tracker yang seperti namanya dapat mengikuti pergerakan matahari sepanjang hari. Dan pada akhirnya saya akan menunjukkan kepada anda perbezaan penuaian tenaga antara panel solar yang dipasang pelacak solar