Isi kandungan:

- Langkah 1: Tambahkan Sumber dan Pilih "Tambah atau Buat Sumber Simulasi

- Langkah 2: Buat Fail Dipanggil Enable_sr_tb

- Langkah 3: Buat Fail Testbench

- Langkah 4: Tetapkan Enable_sr_tb Sebagai Tingkat Atas Di Bawah Simulasi

- Langkah 5: Jalankan Simulasi Sintesis & Tingkah Laku

- Langkah 6: Nilaikan Hasil Simulasi

- Pengarang John Day day@howwhatproduce.com.

- Public 2024-01-30 11:11.

- Diubah suai terakhir 2025-01-23 15:01.

Saya telah melakukan projek simulasi ini untuk kelas dalam talian. Projek ini ditulis oleh Verilog. Kami akan menggunakan simulasi di Vivado untuk memvisualisasikan bentuk gelombang di allow_sr (enabled digit) dari projek jam tangan yang dibuat sebelumnya. Sebagai tambahan, kami akan menggunakan tugas sistem untuk memaparkan kesalahan yang dibuat oleh kami dalam reka bentuk.

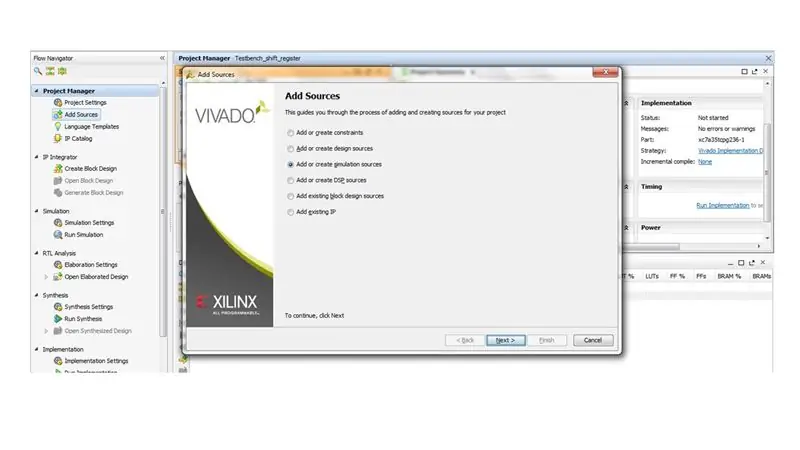

Langkah 1: Tambahkan Sumber dan Pilih "Tambah atau Buat Sumber Simulasi

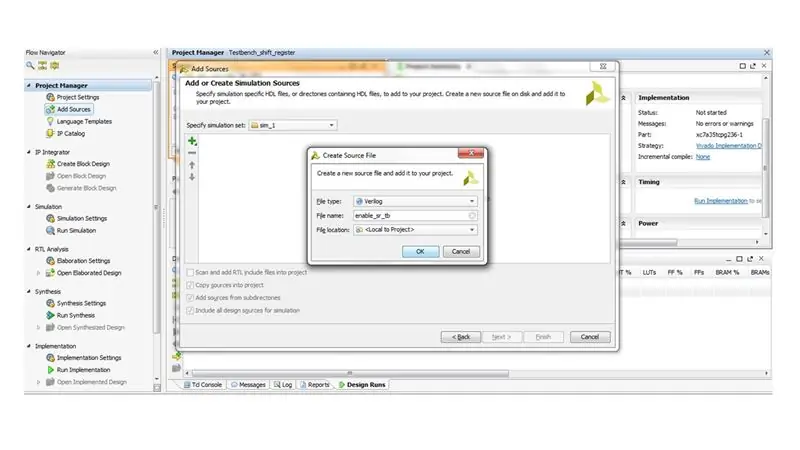

Langkah 2: Buat Fail Dipanggil Enable_sr_tb

Langkah 3: Buat Fail Testbench

1. Import modul allow_sr dari projek jam tangan. Itulah fail yang ingin kita simulasi

2. Buat modul testbench enable_sr_tb ();

3. Masukkan input dan output modul allow_sr (). Ingatlah bahawa input untuk allow_sr kini dalam jenis daftar sementara output menjadi jenis bersih.

4. Instantiate unit yang diuji (uut) yang merupakan allow_sr

5. Hasilkan jam yang tempoh (T) ialah 20ns

6. Gunakan pernyataan bersyarat untuk membuat sistem pemeriksaan ralat. Dalam contoh ini, kami ingin memeriksa sama ada terdapat lebih daripada satu digit yang aktif.

Catatan: Dalam fail allow_sr () yang asal, kita harus memulakan corak sebagai 4'b0011 sehingga ada dua digit yang aktif untuk membuat ralat

7. Gunakan paparan $ task system untuk menunjukkan kesalahan

8. Gunakan tugas sistem $ finish untuk menyelesaikan simulasi pada masa 400ns

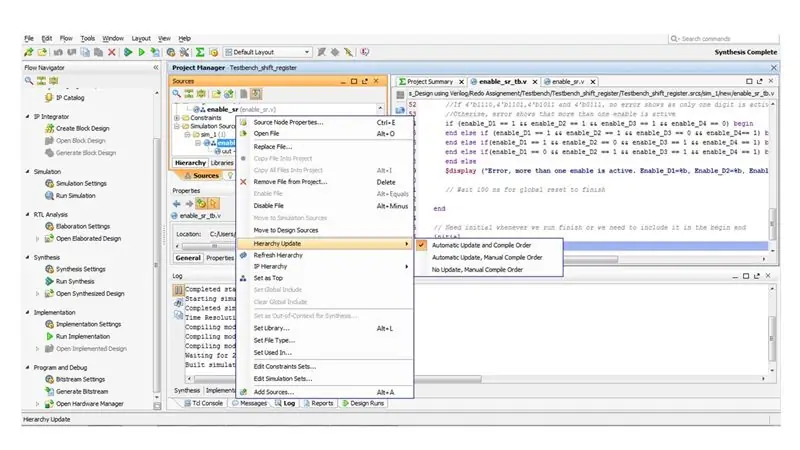

Langkah 4: Tetapkan Enable_sr_tb Sebagai Tingkat Atas Di Bawah Simulasi

Langkah 5: Jalankan Simulasi Sintesis & Tingkah Laku

- Sebelum menjalankan simulasi tingkah laku, jalankan sintesis untuk memastikan bahawa tidak ada kesalahan sintaks dalam fail testbench dan unit di bawah fail ujian

- Jalankan simulasi tingkah laku

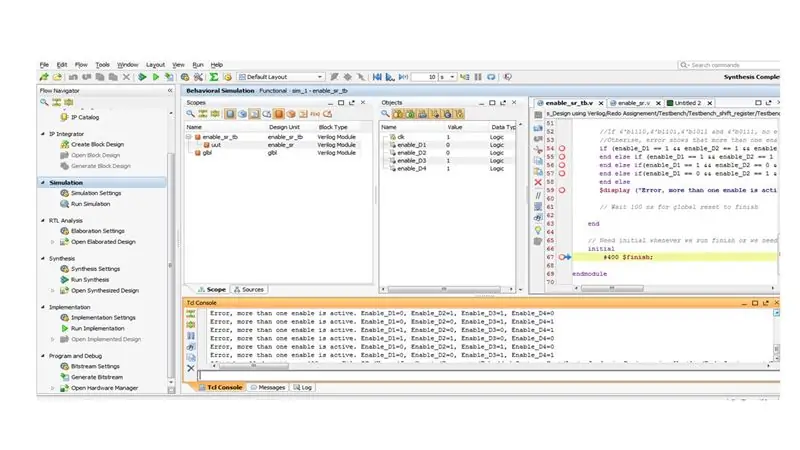

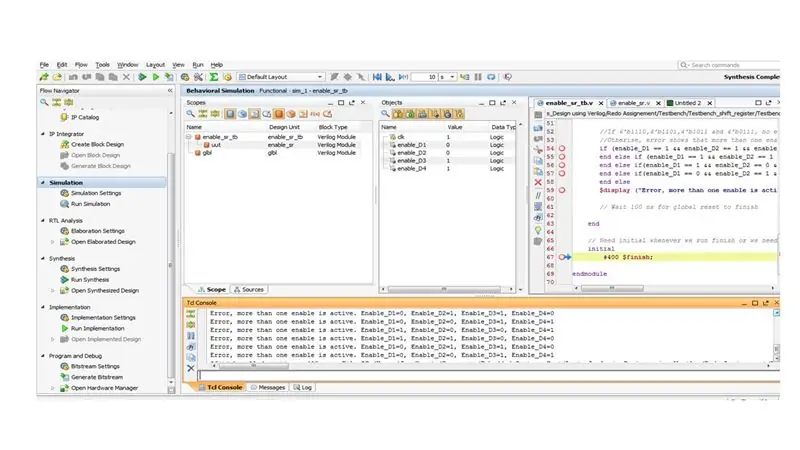

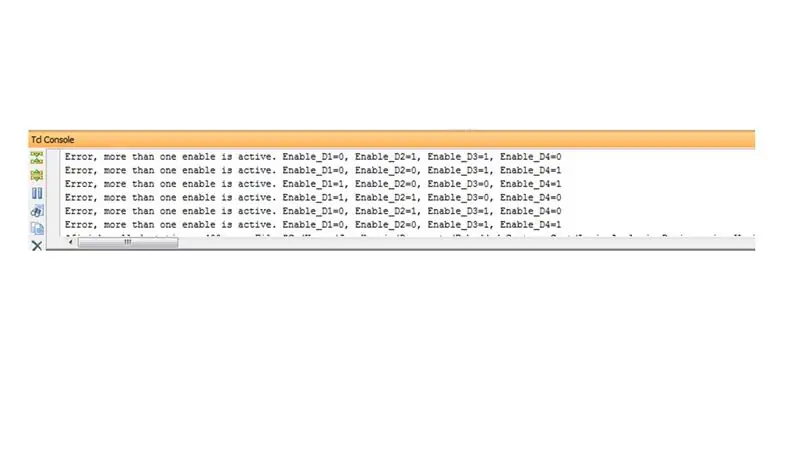

Langkah 6: Nilaikan Hasil Simulasi

Anda akan melihat tetingkap simulasi. Ia mengandungi panel yang berbeza.

Anda akan melihat mesej ralat di panel konsol. Ini menunjukkan lebih daripada satu digit aktif dalam tempoh simulasi.

Anda juga dapat melihat bentuk gelombang dalam skop

Dilampirkan adalah fail projek.

Disyorkan:

Pemerolehan Isyarat ECG Simulasi Menggunakan LTSpice: 7 Langkah

Pemerolehan Isyarat ECG Simulasi Menggunakan LTSpice: Keupayaan jantung untuk mengepam adalah fungsi isyarat elektrik. Doktor boleh membaca isyarat ini pada ECG untuk mendiagnosis pelbagai masalah jantung. Sebelum isyarat dapat disiapkan dengan betul oleh doktor, ia mesti disaring dengan betul dan

ECG automatik: Amplifikasi dan Simulasi Penapis Menggunakan LTspice: 5 Langkah

ECG automatik: Amplifikasi dan Simulasi Penapis Menggunakan LTspice: Ini adalah gambar peranti terakhir yang akan anda bina dan perbincangan yang mendalam mengenai setiap bahagian. Juga menerangkan pengiraan untuk setiap peringkat. Imej menunjukkan gambarajah blok untuk peranti ini Kaedah dan Bahan: Objektif pr

SIMULASI MESIN DISINFEKSI MENGGUNAKAN TINKERCAD: 6 Langkah

SIMULASI MESIN DISINFEKSI MENGGUNAKAN TINKERCAD: Dalam hal ini kita akan melihat bagaimana membuat simulasi Mesin Pembasmian Kuman, Hubungi kurang Pembersih Automatik adalah mesin pembasmi kuman kerana kita tidak akan menggunakan tangan kita untuk mengoperasikan mesin dan bukannya sensor sensor inframerah Proximity

Open Loop Opamp Simulasi Menggunakan Aplikasi EveryCiruit: 5 Langkah

Open Loop Opamp Simulation Menggunakan EveryCiruit App: EveryCircuit adalah salah satu platform simulasi 'yang terbaik' untuk elektronik. Ia mempunyai laman web dan Aplikasi. Ini boleh digunakan untuk versi Android. Tetapi tepat untuk versi web juga. Mengenai Instructable ini: Opamp atau Operational Amplifier adalah

Cara Menggunakan Terminal Mac, dan Cara Menggunakan Fungsi Utama: 4 Langkah

Cara Menggunakan Terminal Mac, dan Cara Menggunakan Fungsi Utama: Kami akan menunjukkan kepada anda cara membuka Terminal MAC. Kami juga akan menunjukkan kepada anda beberapa ciri dalam Terminal, seperti ifconfig, mengubah direktori, mengakses fail, dan arp. Ifconfig akan membolehkan anda memeriksa alamat IP anda, dan iklan MAC anda